Copyright by Jian Chen 2011

The Dissertation Committee for Jian Chen certifies that this is the approved version of the following dissertation:

# Resource Management for Efficient Single-ISA Heterogeneous Computing

| Committee:                   |  |

|------------------------------|--|

|                              |  |

| Lizy Kurian John, Supervisor |  |

| Earl E. Swartzlander, Jr.    |  |

| Joydeep Ghosh                |  |

| David Z. Pan                 |  |

| Lieven Eeckhout              |  |

## Resource Management for Efficient Single-ISA Heterogeneous Computing

$\mathbf{b}\mathbf{y}$

Jian Chen, B.E.; M.E.; M.S.E.

#### **DISSERTATION**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm May} \ 2011$

### Acknowledgements

I am grateful for many people who helped me throughout my journey of PhD study, and I would like to take this opportunity to acknowledge their efforts.

First of all, I would like to thank my advisor, Lizy K. John, for providing me with the freedom and the resources to do high-quality research and for teaching me valuable lessons in research and beyond.

I would also like to thank all the members of LCA group. I especially thank Dimitris Kaseridis for establishing the simulation platform and making the group a fun place to work at, Arun Nair for the wonderful collaboration, Ciji Isen for bringing some software aspects in my research, Jeff Stuecheli for sharing his industry perspectives, and Karthik Ganesan, Muhammad U. Farooq, Faisal Iqbal, Jungho Jo, YoungTaek Kim for their valuable feedbacks on my papers and presentations.

Very special thanks to Dong Li for the intelligent discussions on research as well as the sincere sharing of life stories, which made the stressful PhD life a bit easier.

Many thanks to Lieven Eeckhout, Earl Swartzlander, Joydeep Gosh and David Pan for serving in my PhD committee.

Finally, I would like to thank my parents, Zelin Hu and Yuehuai Chen, my girlfriend, Shifang Liu, for their unconditional support throughout my PhD study. Without their encouragement and dedication, I would not have completed this dissertation.

**Resource Management for Efficient Single-ISA Heterogeneous Computing**

Publication No.\_\_\_\_\_

Jian Chen, Ph.D.

The University of Texas at Austin, 2011

Supervisor: Lizy Kurian John

Single-ISA Heterogeneous Multi-core Processors (SHMPs) have become increasingly

important due to their potential to significantly improve the execution efficiency for

diverse workloads and thereby alleviate the power density constraints in Chip

Multiprocessors (CMPs). The importance of SHMP is further underscored by the fact

that manufacturing defects and process variation could also cause single-ISA

heterogeneity in CMPs even though the CMP is originally designed as homogeneous.

However, to fully exploit the execution efficiency that SHMP has to offer, programs

have to be efficiently mapped/scheduled to the appropriate cores such that the hardware

resources of the cores match the resource demands of the programs, which is challenging

and remains an open problem.

This dissertation presents a comprehensive set of off-line and on-line techniques

that leverage analytical performance modeling to bridge the gap between the workload

diversity and the hardware heterogeneity. For the off-line scenario, this dissertation

presents an efficient resource demand analysis framework that can estimate the resource

vi

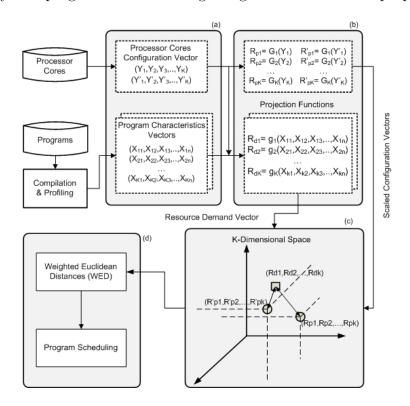

demands of a program based on the inherent characteristics of the program without using any detailed simulation. Based on the estimated resource demands, this dissertation further proposes a multi-dimensional program-core matching technique that projects program resource demands and core configurations to a unified multi-dimensional space, and uses the weighted Euclidean distance between these two to identify the matching program-core pair.

This dissertation also presents a dynamic and predictive application scheduler for SHMPs. It uses a set of hardware-efficient online profilers and an analytical performance model to simultaneously predict the application's performance on different cores. Based on the predicted performance, the scheduler identifies and enforces near-optimal application assignment for each scheduling interval without any trial runs or off-line profiling. Using only a few kilo-bytes of extra hardware, the proposed heterogeneity-aware scheduler improves the weighted speedup by 11.3% compared with the commodity OpenSolaris scheduler and by 6.8% compared with the best known research scheduler.

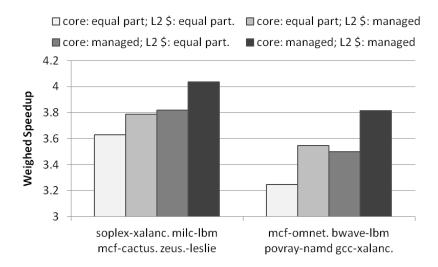

Finally, this dissertation presents a predictive yet cost effective mechanism to manage intra-core and/or inter-core resources in dynamic SHMPs. It also uses a set of hardware-efficient online profilers and an analytical performance model to predict the application's performance with different resource allocations. Based on the predicted performance, the resource allocator identifies and enforces near optimum resource partitions for each epoch without any trial runs. The experimental results show that the proposed predictive resource management framework could improve the weighted speedup of the CMP system by an average of 11.6% compared with the equal partition scheme, and 9.3% compared with existing reactive resource management scheme.

# Table of Contents

| Ackno   | owledgements                                                           | V    |

|---------|------------------------------------------------------------------------|------|

| Abstra  | act                                                                    | vi   |

| List of | Tables                                                                 | xii  |

| List of | Figures                                                                | xiii |

| Chap    | ter 1. Introduction                                                    | 1    |

| 1.1     | Single-ISA Heterogeneous Multi-core Processor                          | 1    |

| 1.2     | The Problem: Gap between Workload Diversity and Hardware Heterogeneity | 2    |

| 1.3     | Proposed Approach                                                      | 4    |

| 1.4     | Thesis Statement                                                       | 5    |

| 1.5     | Contributions                                                          | 5    |

| 1.6     | Dissertation Organization                                              | 7    |

| Chapt   | ter 2. Background and Related Work                                     | 9    |

| 2.1     | Related Research on Creating SHMP                                      | 9    |

| 2.2     | Related Research on Application Scheduling in Static SHMP              | 11   |

| 2.3     | Related Research on Dynamic Resource Management                        | 12   |

| 2.4     | Related Research on Performance Modeling                               | 14   |

| Chapt   | ter 3. Analytical Performance Modeling                                 | 16   |

| 3.1     | Basic Analytical Model                                                 | 16   |

| 3.2     | Extended Performance Model                                             | 18   |

|         | 3.2.1 Impact of Limited Functional Units                               | 19   |

|         | 3.2.2 Impact of Operating Frequency                                    | 21   |

|         | 3.2.3 Impact of L2 Cache Size                                          | 22   |

|         | 3.2.4 Impact of Memory-Level Parallelism                               | 23   |

|         | 3.2.5 Impact of Co-executing Threads                                   | 24   |

| 3.3     | Summary                                                                | 27   |

| Chap | ter 4. Experiment Methodology                                       | 28 |

|------|---------------------------------------------------------------------|----|

| 4.1  | Simulation Platform                                                 | 28 |

|      | 4.1.1 Simulation Platform for Resource Demand Analysis              | 28 |

|      | 4.1.2 Simulation Platform for Program-core Mapping                  | 30 |

|      | 4.1.3 Simulation Platform for Application Scheduling in Static SHMP | 31 |

|      | 4.1.4 Simulation Platform for Resource Management in Dynamic SHMP   | 32 |

| 4.2  | Workloads                                                           | 34 |

|      | 4.2.1 Workloads for Program Resource Demand Analysis                | 34 |

|      | 4.2.2 Workloads for Program-core Mapping                            | 34 |

|      | 4.2.3 Workloads for Application Scheduling in Static SHMP           | 34 |

|      | 4.2.4 Workloads for Resource Management in Dynamic SHMP             | 35 |

| 4.3  | Metrics                                                             | 37 |

| Chap | ter 5. Program Resource Demand Analysis                             | 38 |

| _    | Resource Demand Definition                                          | 38 |

|      | Overview of the Framework                                           | 39 |

|      | Performance Modeling                                                | 40 |

|      | Demand on Multiple Resources                                        | 41 |

|      | Demand on Memory Bandwidth                                          | 43 |

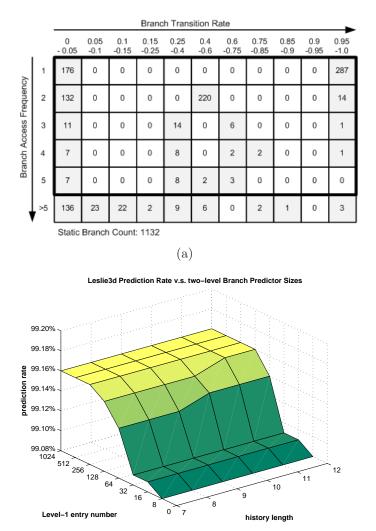

|      | Demand on Branch Predictor Size                                     | 45 |

|      | Evaluation                                                          | 48 |

|      | 5.7.1 Model Accuracy                                                | 48 |

|      | 5.7.2 Accuracy of Resource Demand Estimation                        | 52 |

|      | 5.7.2.1 Single-Resource Demand Estimation                           | 52 |

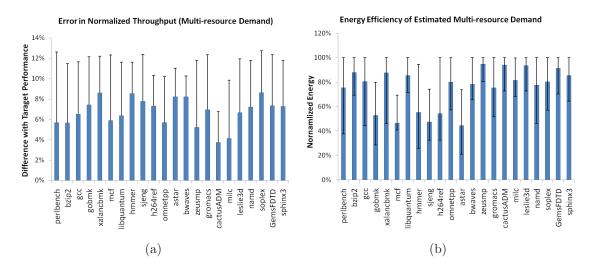

|      | 5.7.2.2 Multi-Resource Demand Estimation                            | 56 |

|      | 5.7.3 Complexity Analysis                                           | 58 |

| 5.8  | Summary                                                             | 59 |

| Chan | ter 6. Program-core Mapping in Static SHMP                          | 60 |

| 6.1  | Framework                                                           | 60 |

| 6.2  | Projection Function                                                 | 62 |

| 6.3  | Weight Assignment                                                   | 66 |

| 6.4  | Mapping Heuristic                                                   |    |

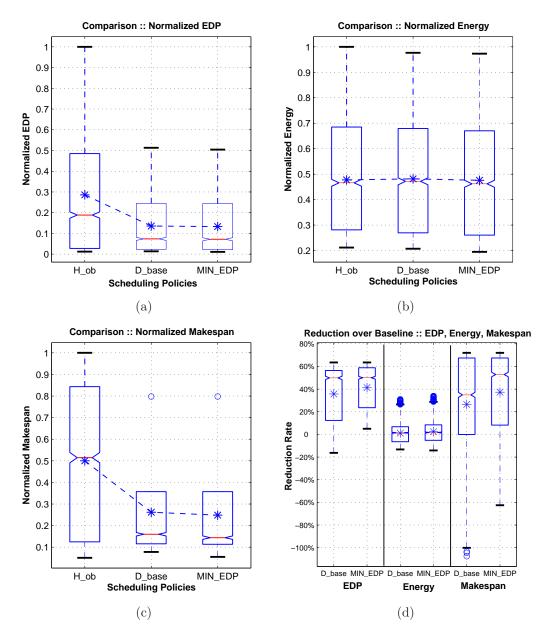

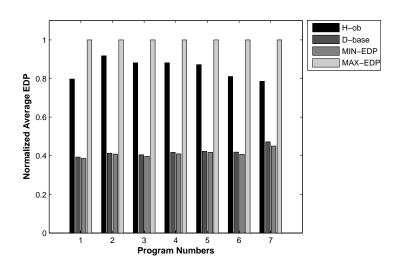

| 6.5  | Evaluation                                                          | 71 |

|      | Summary                                                             | 74 |

| Chapt        | ter 7. Pi  | redictive Scheduling in Static SHMP             | <b>75</b> |

|--------------|------------|-------------------------------------------------|-----------|

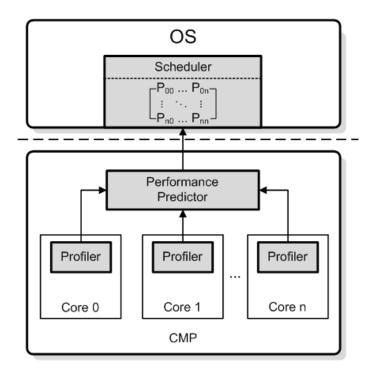

| 7.1          | Schedulin  | ng Framework                                    | 75        |

| 7.2          | Performa   | nce Modeling                                    | 77        |

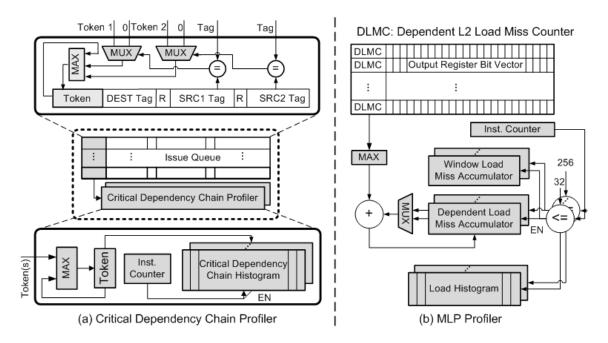

| 7.3          | Online P   | rofilers                                        | 77        |

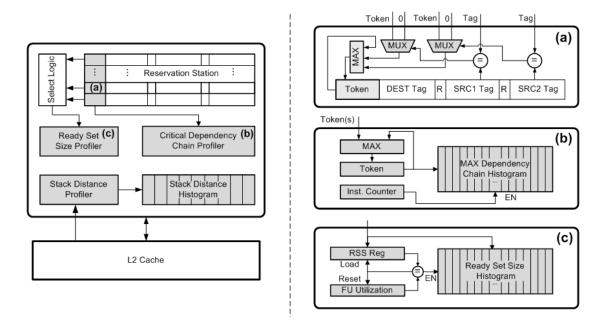

|              | 7.3.1 Cr   | ritical Dependency Chain Profiler               | 77        |

|              | 7.3.2 Re   | eady Set Size Profiler                          | 78        |

|              | 7.3.3 St   | ack Distance Profiler                           | 80        |

|              | 7.3.4 Pr   | rofiling for Other Parameters                   | 80        |

|              | 7.3.5 Ha   | ardware Cost Analysis                           | 81        |

| 7.4          | Schedulii  | ng Heuristics                                   | 82        |

| 7.5          | Evaluation | on                                              | 85        |

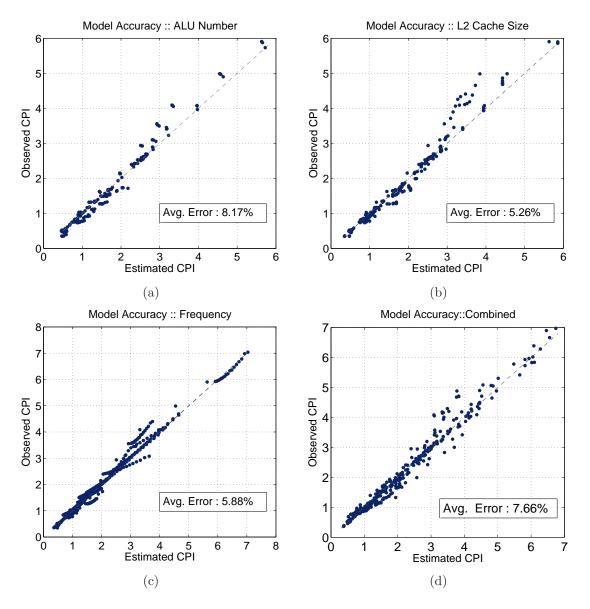

|              | 7.5.1 M    | odel Accuracy                                   | 85        |

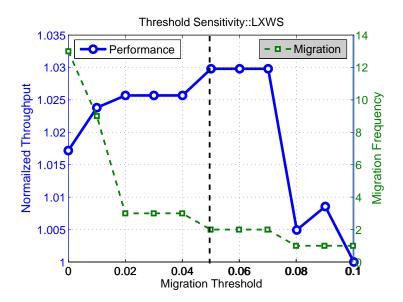

|              | 7.5.2 M    | figration Threshold                             | 87        |

|              | 7.5.3 Pe   | erformance                                      | 87        |

| 7.6          | Summary    | y                                               | 94        |

| Chapt        | ter 8. Pi  | redictive Resource Coordination in Dynamic SHMP | 95        |

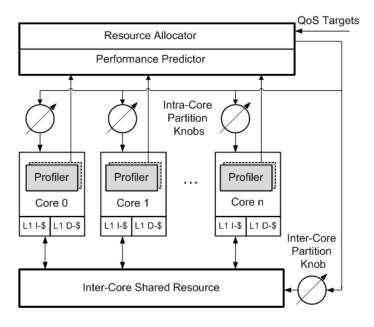

| 8.1          |            | Coordination Framework                          | 97        |

| 8.2          | Performa   | nnce Prediction                                 | 99        |

| 8.3          | On-line I  | Profiling Support                               | 102       |

|              |            | ritical Dependency Chain Profiler               |           |

|              | 8.3.2 M    | LP Profiler                                     | 103       |

| 8.4          | Resource   | Coordination Algorithm                          | 104       |

| 8.5          | Impleme    | entation Cost Analysis                          | 108       |

| 8.6          | Evaluation | on                                              | 109       |

|              | 8.6.1 M    | odel Accuracy                                   | 110       |

|              | 8.6.2 Ep   | ooch Size Sensitivity                           | 110       |

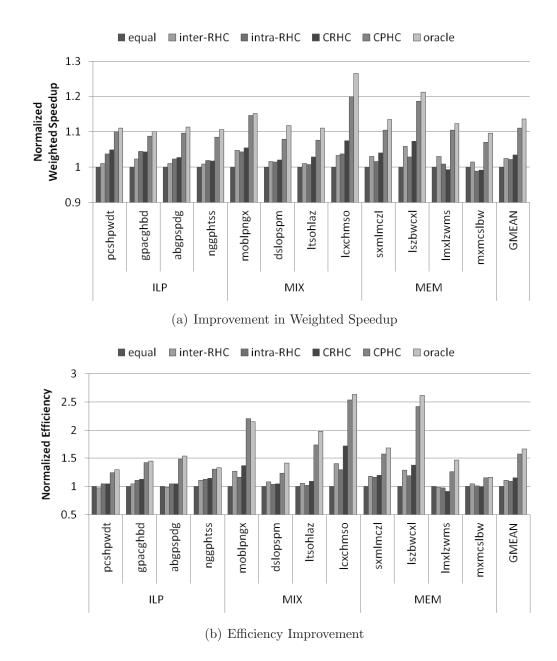

|              | 8.6.3 Pe   | erformance & Efficiency                         | 113       |

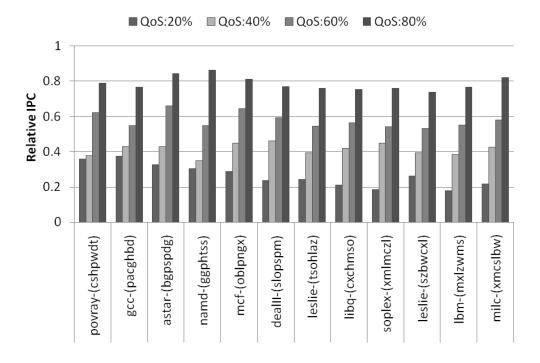

|              | 8.6.4 Qo   | oS Enforcement                                  | 115       |

| 8.7          | Summary    | y                                               | 116       |

| Chant        | ter 9.     | onclusions and Future Research Directions       | 117       |

| _            | Conclusio  |                                                 |           |

|              |            | esearch Directions                              |           |

| , . <u>-</u> |            | proving the Efficiency of On-line Profilers     |           |

|              |            | spanding the Types of Heterogeneous Resources   |           |

Bibliography 121

## List of Tables

| 3.1 | Estimation of Effective Average Execution Rate for 2-Way SMT     | 26  |

|-----|------------------------------------------------------------------|-----|

| 4.1 | Configuration Options                                            | 29  |

| 4.2 | Configurations of Each Core                                      | 30  |

| 4.3 | Nominal Configurations of the CMP system                         | 32  |

| 4.4 | Configurations of the CMP system                                 | 32  |

| 4.5 | Configurations of the CMP system                                 | 33  |

| 4.6 | Workloads and Their Characteristics                              | 35  |

| 4.7 | Workloads and Their Characteristics                              | 36  |

| 5.1 | Evaluation of The Demand Estimation for Branch Predictor Size    | 56  |

| 6.1 | Projection Functions                                             | 64  |

| 6.2 | Correlation Coefficient between EDP and WED                      | 71  |

| 7.1 | Hardware Cost of the Online Profilers for Application Scheduling | 82  |

| 8.1 | Hardware Cost of the Online Profilers for Resource Management    | 109 |

# List of Figures

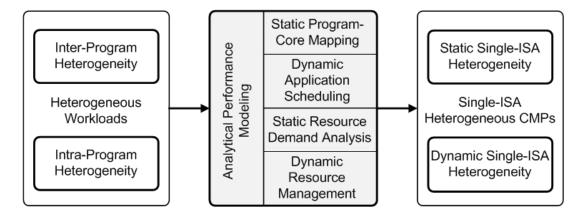

| 1.1 | Overview of the proposed research                                                                  | 5  |

|-----|----------------------------------------------------------------------------------------------------|----|

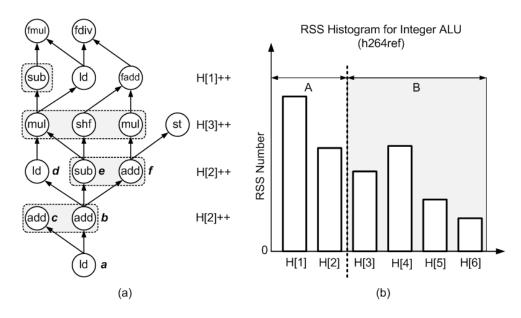

| 3.1 | The instruction ready set and the RSS histogram                                                    | 20 |

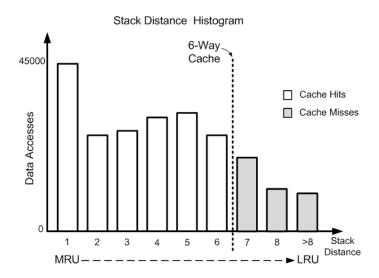

| 3.2 | Stack Distance Histogram of SPEC CPU2006 program xalancbmk                                         | 23 |

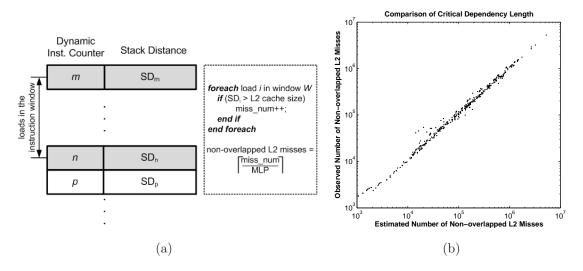

| 3.3 | MLP Modeling                                                                                       | 25 |

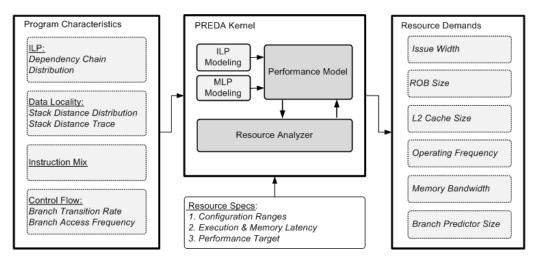

| 5.1 | The PREDA framework                                                                                | 40 |

| 5.2 | Branch predictor size demand estimation                                                            | 46 |

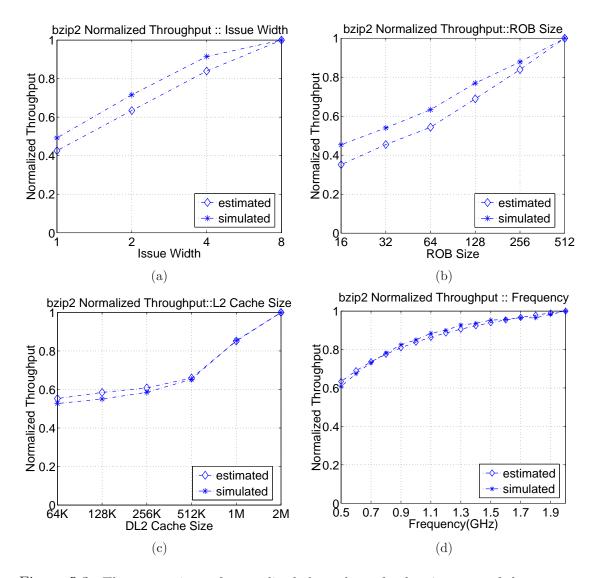

| 5.3 | The comparison of normalized throughput for <i>bzip2</i> as one of the resources changes           | 49 |

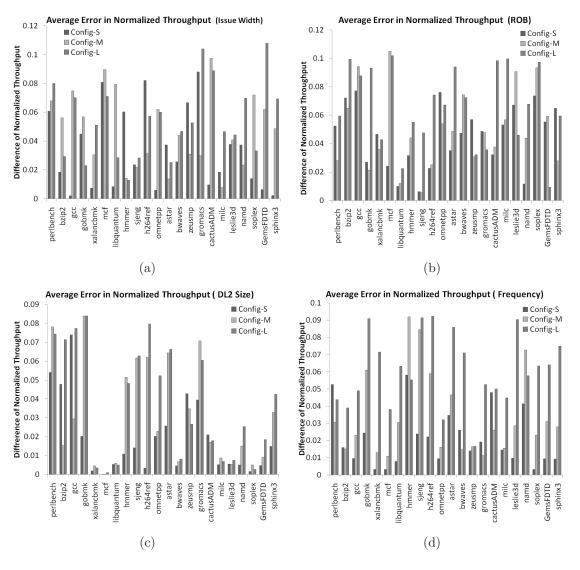

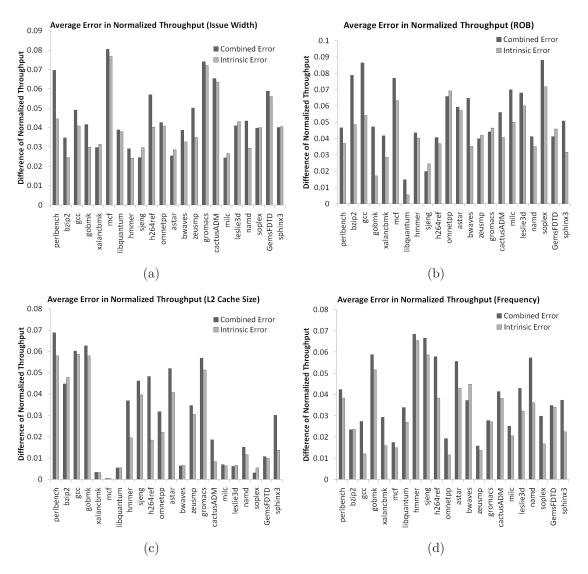

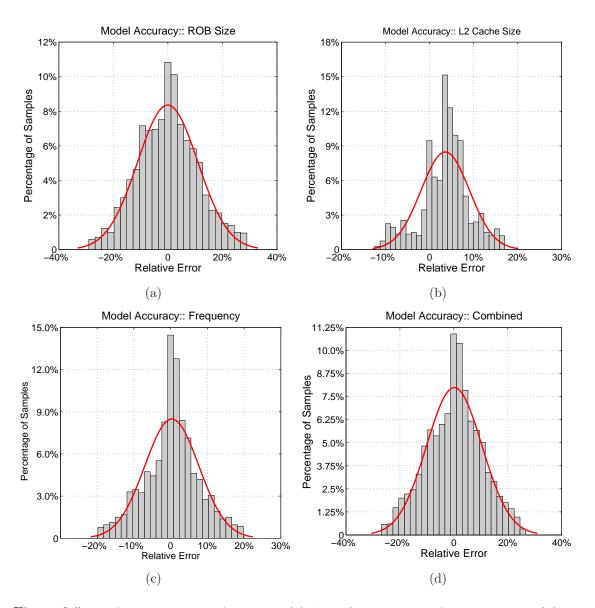

| 5.4 | Average error of the normalized throughput for issue width, ROB size, L2 cache size, and frequency | 50 |

| 5.5 | Comparison of the combined error and the intrinsic error in normalized throughput.                 | 51 |

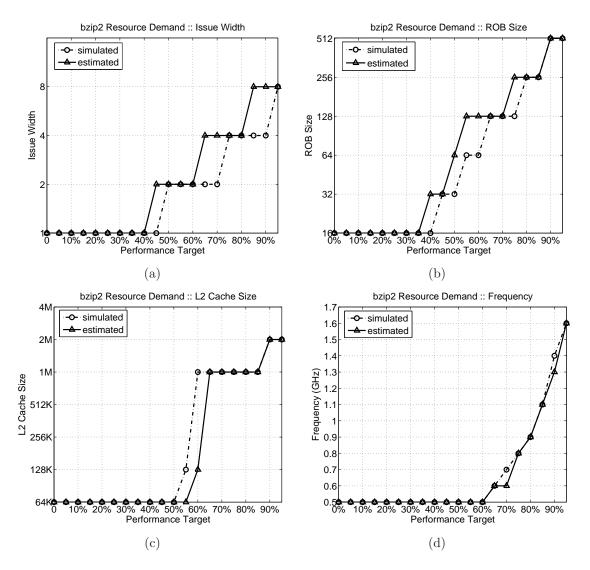

| 5.6 | The accuracy of single-resource demand estimation for bzip2                                        | 53 |

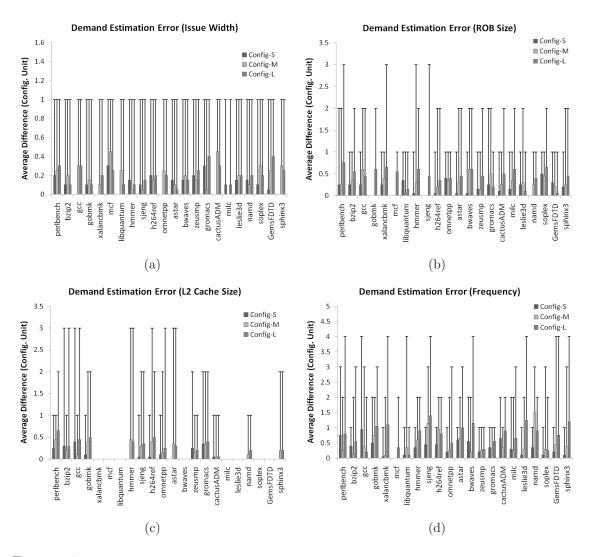

| 5.7 | The error of resource estimation.                                                                  | 54 |

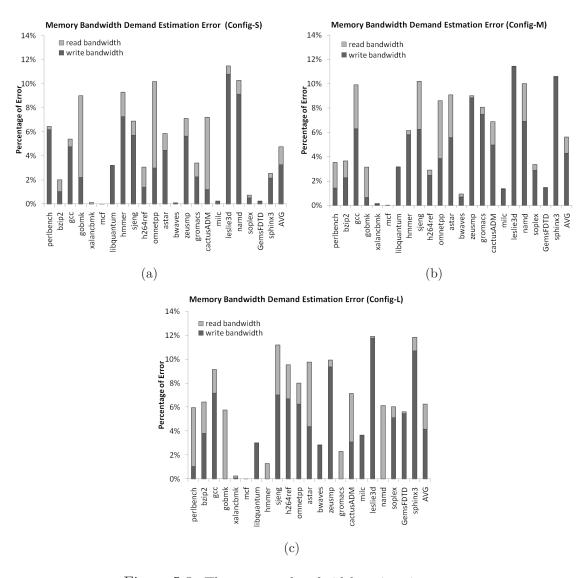

| 5.8 | The memory bandwidth estimation error                                                              | 55 |

| 5.9 | Evaluation of Multi-resource Demand Estimation                                                     | 57 |

| 6.1 | Framework for multidimensional program-core matching                                               | 61 |

| 6.2 | EDP, energy and makespan comparison between different scheduling heuristics                        | 73 |

| 6.3 | Scheduling results for different number of programs                                                | 74 |

| 7.1 | The overview of the PHASE framework                                                                | 76 |

| 7.2 | The structure of the online profilers                                                              | 79 |

| 7.3 | Model Accuracy.                                                                                    | 86 |

| 7.4 | Migration Threshold                                                                                | 88 |

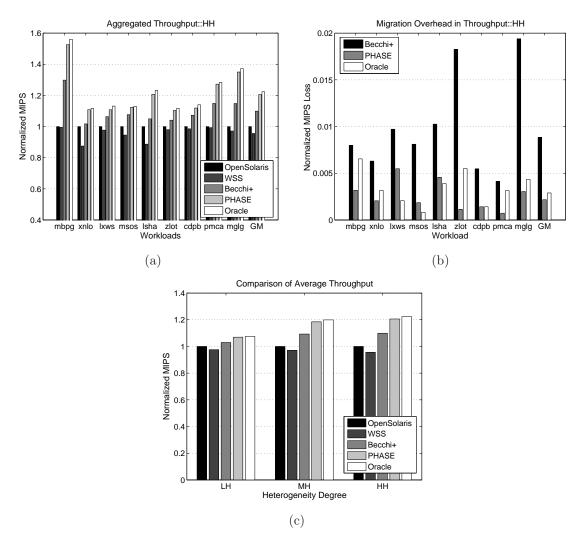

| 7.5 | Comparison of throughput.                                                                          | 89 |

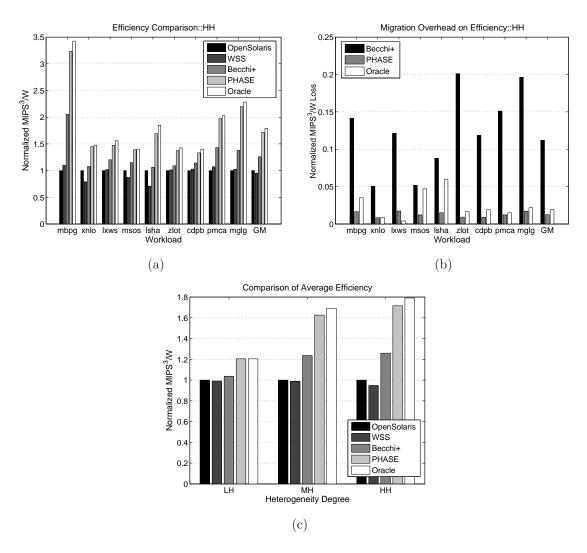

| 7.6 | Comparison of efficiency                                                                           | 91 |

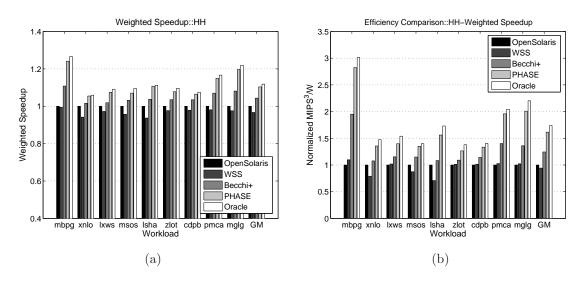

| 7.7 | Comparison of weighted speedup and efficiency                                                      | 92 |

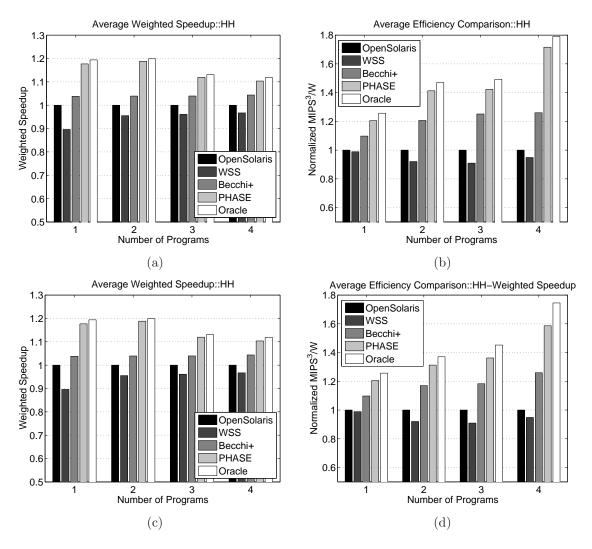

| 7.8 | Average performance and efficiency improvement vs program number.                                  | 93 |

| 8.1 | Comparison of weighted speedup for different resource management                 |

|-----|----------------------------------------------------------------------------------|

|     | policies                                                                         |

| 8.2 | The overview of the multiple resource management framework 98                    |

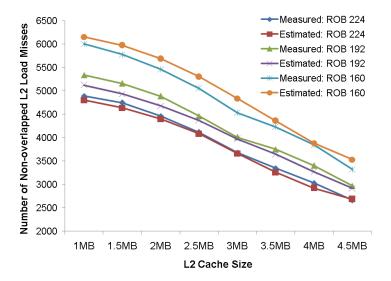

| 8.3 | The comparison of estimated and measured non-overlapped L2 load misses           |

| 8.4 | The structure of the online profilers                                            |

| 8.5 | Performance Model Accuracy                                                       |

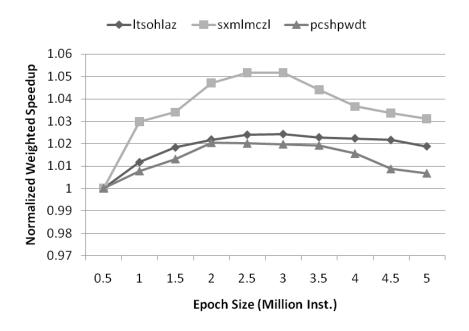

| 8.6 | Performance impact of epoch size                                                 |

| 8.7 | Performance and efficiency comparison for different resource management policies |

| 8.8 | QoS targets enforcement                                                          |

## Chapter 1

#### Introduction

Chip Multiprocessors (CMP) have become the mainstream computing platform to improve the utilization of the abundant yet ever-increasing on-chip resources

and alleviate the power density constraints. By integrating multiple cores in a single

chip, CMP allows multiple programs or multiple threads to simultaneously execute

on different cores on the same chip, significantly improving the system throughput

and efficiency. However, CMPs composed of homogeneous processor cores still suffer

from inefficiency because they lead to an inevitable dilemma: replicating smaller

cores compromises the throughput of the high-complexity single-threaded applications; whereas replicating larger cores sacrifices the execution efficiency of the lowcomplexity low-priority applications. Therefore, to achieve high efficiency, CMPs

need certain amount of core-level heterogeneity to accommodate or adapt to the

diverse workload requirements.

## 1.1 Single-ISA Heterogeneous Multi-core Processor

Single-ISA Heterogeneous Multi-core Processor (SHMP) [1] emerges as an important and attractive type of CMP that provides the core-level heterogeneity to meet the diverse requirements of the workloads. It consists of cores with the same Instruction-Set Architecture (ISA) yet different configurations, and hence allows any application/task to be executed on any core in the system without modification in the

application binaries. Depending on the runtime configurability of the processor cores, SHMP can be categorized as *Static Single-ISA Heterogeneous Multi-core Processor* or *Dynamic Single-ISA Heterogeneous Multi-core Processor*.

Static SHMP is statically composed of cores with fixed yet different configurations. Such static heterogeneity can be introduced intentionally by integrating cores with different complexity in a single chip at the design stage or can be caused unintentionally by process variation and hardware defects during the manufacturing stage. Either way, it relies on an appropriate scheduling scheme to map the program to the processor core that matches the program's resource demands [2][3]. On the other hand, dynamic SHMP is realized by dynamically reconfiguring the cores as well as other on-chip resources, such as L2 cache sizes, to meet the need of the applications. Examples of such SHMP include Tflex [4] and Core Fusion [5]. Such SHMPs are able to meet the application resource demand changes at a finer granularity during runtime, yet their hardware adaptation still relies on the workload heterogeneity being properly translated to the corresponding hardware resource demands.

## 1.2 The Problem: Gap between Workload Diversity and Hardware Heterogeneity

In static SHMPs, mapping the workload diversity to the hardware heterogeneity is achieved by heterogeneity-aware application scheduling; whereas in dynamic SHMPs, it is typically achieved by runtime resource adaptation. However, in both cases, the existing methods are severely constrained by their inefficiency, poor scalability, and inability to enforce performance objectives.

**Issues on Efficiency**: The conventional approach for heterogeneity-aware

application scheduling relies on tentative runs to explore the appropriate applicationcore mapping [2][6]. Specifically, this approach tentatively executes the application

on different cores, each for a short period of time, and then schedules the program

to the optimum core based on the sampled Energy-Delay Product (EDP) during

the tentative runs. This method suffers inefficiency from the trial runs as they incur

significant power and performance overhead in moving around the architecture states

and data sets, potentially negating the benefit of the improvement in application

scheduling. Similarly, the conventional method for dynamic resource adaptation

also uses the trial-and-error approach to explore the appropriate resource allocation,

which also causes inefficiency because a large amount of execution time is spent in

exploring the trial resource allocations.

Issues on Scalability: The trial-and-error application scheduling in static SHMPs is only feasible for a relatively small number of cores, because the number of trial runs for exploring all scheduling options grows almost exponentially as the number of heterogeneous cores increases. Similarly, for dynamic resource adaptation, the time needed for tentative runs becomes almost intractable for a large reconfiguration space, resulting in slow adaptation and poor performance.

Issues on Performance Objective Enforcement: Providing performance isolation for the co-executing applications and enforcing the given performance objectives are becoming increasingly important as CMPs expand their usage toward service-oriented computing, server consolidation and virtualization [7]. However, dynamic resource adaptation using tentative runs takes long latency to find the appropriate resource allocations for the system performance objectives. Such a long response latency may occupy a significant portion of the program phase, or even

exceed the phase duration, resulting in inefficiency or even inability to provide performance level guarantees.

As a result, to unleash the full potential for heterogeneous computing, there is an urgent need of efficient and scalable techniques that can translate the workload diversity to the hardware heterogeneity, and enforce system performance objectives. To this end, this dissertation presents and evaluates a set of techniques for analyzing the resource demands and thereby managing multiple interactive resources.

#### 1.3 Proposed Approach

Whether it is application scheduling in static SHMP or resource management in dynamic SHMP, efficiently identifying the resource demand of the application is the key step to close the gap between the workload heterogeneity and the hardware heterogeneity. To do so, this dissertation proposes to leverage analytical performance modeling and micro-architecture independent characteristics for resource demand identification, as shown in Figure 1.1. Unlike the regression models [8][9] or the neural network models [10], the analytical performance model does not require training which significantly boosts the efficiency in exploring the configuration space both off-line and on-line. Using micro-architecture independent characteristics also allows the resource demand identification to be isolated from any partial simulations, not only speeding-up the process of resource demand analysis, but also enabling on-line performance prediction.

Based on the identified resource demands, this dissertation presents a multidimensional matching technique [11] for off-line program-core mapping, and a performance prediction scheme for on-line application scheduling to improve the computing

Figure 1.1: Overview of the proposed research. The grey boxes highlight the scope of this research.

efficiency in static SHMP. On the other hand, using the proposed analytical model, this dissertation also presents a comprehensive yet cost-effective resource management framework that can coordinate multiple shared resources while simultaneously enforcing Quality-of-Service (QoS) performance objectives.

#### 1.4 Thesis Statement

The combination of analytical performance modeling and micro-architecture independent characteristics provides an attractive platform for program resource demand analysis, which further enables efficient and scalable application scheduling and multiple resource management for the single-ISA heterogeneous computing environment.

#### 1.5 Contributions

This dissertation makes the following major contributions:

1. This dissertation presents an analytical model based on program character-

istics such as Instruction Level Parallelism (ILP), Memory Level Parallelism (MLP) and branch predictability. Unlike existing analytical models [12][13], which require simulations on caches and branch predictors, this proposed model avoids any partial detailed simulation; yet it is still able to accurately model the performance trend for different hardware configurations. The decoupling from detailed simulation not only makes this model efficient in estimating the resource demand off-line, but also allows it to be applied in proactive on-line resource management. This dissertation also encapsulates the analytical model and the resource demand estimation algorithms into an integrated framework called *Program REsource Demand Analyzer* (PREDA), which automatically estimates a broad set of resource demands for a workload. Compared with the framework using a state-of-the-art analytical model [13], this framework achieves significant speedup in estimating multi-resource demands.

- 2. This dissertation presents an off-line program-core mapping framework for static heterogeneous CMPs. The proposed framework projects the core configurations and the programs resource demands into a unified multi-dimensional space, where the program-core matching can be easily identified with weighted Euclidean distances. This dissertation demonstrates that the weighted Euclidean distance is strongly correlated with EDP, hence can be used to guide program scheduling in heterogeneous multicores.

- 3. This dissertation builds a comprehensive yet cost-effective dynamic on-line profiler, and a performance predictor that utilizes the online profile to accurately predict the performance of cores with different configurations on multiple resources. Based on the proposed performance predictor, this dissertation further

proposes a framework for dynamic heterogeneity-aware application scheduling. This scheduling framework eliminates the need of trial-runs or off-line profiling, yet can dynamically and efficiently adapt to program phases. Experimental results show that the proposed approach significantly improves the throughput and efficiency compared with the commodity *OpenSolaris* scheduler and with the best known research scheduler.

4. This dissertation presents a framework for multiple resource management based on the proposed performance model. By using a set of on-line profilers, the performance model is able to predict the performance of the running applications for different resource allocations of both inter-core an intra-core resources, and hence fundamentally eliminating the need of trial-runs or training required for conventional dynamic resource management schemes. This framework is also able to efficiently translate system performance specification to the resource usages, hence it allows the enforcement of QoS performance objectives when multiple interacting resources are reconfigured.

## 1.6 Dissertation Organization

The rest of the dissertation is organized as follows: Chapter 2 gives background and the related work in this area. Chapter 3 presents the details of the analytical performance model. Chapter 4 describes the experiment platforms, workloads as well as the metrics employed in this dissertation. Chapter 5 shows the mechanism for estimating program resource demands using the proposed performance model. Chapter 6 demonstrates the framework of off-line program-core mapping in static SHMP. Chapter 7 presents the framework for dynamic and predictive application

scheduling in static SHMP. Chapter 8 shows the mechanism for predictive coordination of multiple interacting resources in dynamic SHMP. Chapter 9 summarizes of the key results and insights presented in the dissertation, and proposes the directions for future research.

## Chapter 2

## Background and Related Work

#### 2.1 Related Research on Creating SHMP

Single-ISA heterogeneous multi-core architecture was initially proposed by Kumar, et al. [2] as an attractive option for power-efficient computing. Their proposed heterogeneous multicore processor is composed of legacy Alpha cores with different complexities, effectively amortizing the design and verification effort. IBM CELL processor is another variant of heterogeneous multicore processor, which combines a PowerPC Core with eight Synergistic Processing Elements (SPE) [14]. Although the core and SPE uses different instruction sets, the CELL processor does underscore the importance of using heterogeneity or hardware specialization to boost system efficiency.

Besides the intentionally introduced hardware heterogeneity, single-ISA heterogeneity can also be unintentionally introduced by process variation and manufacturing defects. Process variation is defined as a divergence in the parameters of the fabricated transistors from their nominal values, both within dies (WID) and die-to-die (D2D) [15]. It occurs due to random dopant fluctuations and shortcomings of lithographic processes, and could significantly affect the threshold voltage of transistors. ITRS [16] reports that the  $3\sigma$  intra-die variation of a transistor's threshold voltage and effective channel length can be as large as 42% and 12% in 45nm technology, and is expected to be worsen as the technology scales down further. The

variation on these parameters directly impacts the switching speed of the transistors, which further causes the maximum operating frequency of the processor to deviate from its nominal value. In a multi-core processor, this implies that different cores may need to operate at different maximum frequencies.

Besides process variation, hard faults are another important issue in manufacturing process. They are caused by imprecise calibration of equipment, contaminants in materials, as well as particle impurities in the air [17], and could incur functional failures in parts of the processors, resulting in expensive yield loss. It is expected that the yield loss will be exacerbated as the transistor density and die size increase, and needs to be carefully controlled. To mitigate yield loss, industry typically leverages the redundancy in processor components such as SRAM arrays, functional units and queues, and recovers faulty processors by disabling some of the defective yet non-critical units [17]. These rescued processors are fully functional, albeit with reduced performance due to the reduction in certain hardware resources. That said, not all faulty units are suitable for this yield-enhancing technique: faults in critical units, such as control units, could cause complete failure of the processor, and faults in Reorder Buffer (ROB) or load/store queue, may require complex and expensive hardware to recover the functionality. Hence, this dissertation focuses on two types of representative resources that can be protected by this yield-enhancing technique, namely, available functional units and L2 cache size. Functional units have their natural redundancy in microprocessors, especially in wide-issue superscalar processors, and have been explored to improve the yield [17]. L2 cache occupies a large amount of chip real estate, and is susceptible to hard faults. While it is typically equipped with redundancy to improve the yield, the occurrence of hard faults may exceed the protection capability. Should this happen, the defective ways in L2 cache can be discovered and disabled during manufacturing test, which results in a smaller, but functional cache.

While the above heterogeneous CMP are static, the singe-ISA heterogeneity in CMP can also be formulated dynamically. Kim, et al. proposed the Tflex architecture [4], which allows simple and low-power cores to be aggregated together dynamically, creating larger, more powerful processors without changing the application binary. Ipek, et al. also present a flexible chip multiprocessor substrate that can dynamically morph multiple cores into a larger processing unit [5] to meet the runtime requirements of the applications.

# 2.2 Related Research on Application Scheduling in Static SHMP

Along the proposal of SHMP, Kumar, et al. [2] also propose a dynamic program scheduling approach based on the sampled EDP during tentative runs. This method tentatively runs the program on different cores, each for a short period of time, and then schedules the program to the optimum core according to the sampled EDP during the tentative runs. The downside of this method is the expensive context switching cost of the tentative runs, which may significantly degrade the overall efficiency of the multi-core system. Becchi, et al. extends Kumar's work by measuring IPC ratios between two different cores to migrate applications [6]. Essentially, this method uses pair-wise program swapping to reduce the number of trial executions. Nevertheless, this method still relies on tentative runs to identify the matching program-core pair, hence suffers from the same limitation as Kumar's method. Beside the extra power overhead, such trial-and-error approaches also incur scalability issues as the number of cores increases. In future many-core chips, sam-

pling a large amount of cores before scheduling the program would be impractical because the extra cost of sampling will exceed the potential gain of core switching.

In contrast to dynamic scheduling, Chen and John [18] present an off-line technique that leverages the inherent program characteristics for the static program mapping. They employ fuzzy logic to calculate the program-core suitability, and use that to guide program scheduling. However, their method is not scalable since the complexity of fuzzy logic increases exponentially as the number of characteristics increases. Recently, the idea of using program characteristics to guide program scheduling was also employed by Shelepov, et al. in their heterogeneity-aware scheduler [3]. Their proposal utilizes reuse distance signatures constructed from off-line profiling to schedule applications to cores with different cache sizes. These off-line approaches can only schedule the application statically, missing opportunities for exploiting changes in program phase. Moreover, the need for off-line profiling and encoding/decoding of the profiled information in the program binary could result in dramatic modification in the interface between OS, compiler and architecture, which limits the applicability of the off-line approach in practice.

### 2.3 Related Research on Dynamic Resource Management

The dynamic SHMP relies on dynamic resource management techniques to detect the resource demand changes and manage the hardware resource accordingly. These techniques usually leverage hardware performance counters to monitor the performance variations on the fly [19] and reactively tune the hardware resources until it meets the demand of the workload [20]. Choi and Yeung [21] improve the SMT resource distribution by directly using the performance feedback to partition

the resources for a specific performance goal. Their method requires a number of trial resource partitions before it learns the appropriate resource distribution, fundamentally limiting its potential for performance improvement. The trial-and-error nature of the process may require many tuning iterations, and could incur significant performance degradation and energy overhead.

Recently, there are some proactive schemes proposed. Cazorla, et al. [22] proposed a DCRA mechanism to dynamically allocate shared resources to each thread in an SMT processor. Their method uses a resource sharing model to estimate the thread's anticipated resource needs, and allocate resources to the thread that utilizes the resource most efficiently. Like other SMT resource sharing policies [23][24], this method improves the SMT performance only *indirectly*, not only potentially missing opportunities for further performance improvement but also unable to control the end performance. Qureshi, et al. proposed cache utility monitor (UMON) to estimate the utility of assigning additional cache ways to an application [25]. Kaseridis, et al. extended this on-line cache monitor for system-level memory bandwidth management [26]. While these works address single resource management, Bitirgen, et al. attempted to manage multiple resources by using on-line machine learning techniques [27]. However, the on-line machine learning model requires periodic training and is hard to implement and validate. In contrast, our proposed model does not require any training and could be applied on-line for both single or multiple resource management.

#### 2.4 Related Research on Performance Modeling

Whether it is application scheduling in static SHMP or resource management in dynamic SHMP, accurate and efficient performance modeling is the key step to identify the program resource demand changes and thereby make adjustments to achieve efficient heterogeneous computing. The performance modeling usually employs analytical models, regression models, or predictive models.

The analytical model is typically based on *interval analysis*, which was used by Karkhanis and Smith for their first-order superscalar processor model [12]. They further leveraged this model to automatically explore the design space for the Pareto-optimal design parameters [28]. Recently, this model was improved by Eyerman, *et al.* for a higher accuracy in performance modeling [13]. However, all of these models rely on detailed simulation of some components, such as caches and branch predictors, to obtain key statistics of the program-microarchitecture interaction. The requirement for partial simulation not only costs time in off-line performance modeling, but also implies that it has to follow the trial-and-error scheme when applying this model for on-line resource management. However, our approach focuses on modeling the performance trend rather than the absolute performance value, and avoids any detailed simulation of any resource component. The decoupling from detailed simulations not only ensures fast off-line resource demand estimation, but also allows this model to be applied in *proactive* on-line resource management.

Both regression models and predictive models are essentially empirical models, which hide the details of program-hardware interactions by fitting high-level equations with the simulated results. The regression model has been applied in estimating the significance of the design parameters and their interactions [8], exploring

the design space [9] as well as analyzing the microarchitectural adaptivity [29]. An artificial neural network (ANN) based predictive model was also proposed by Ipek, et al. for performance prediction [10]. While these empirical models are relatively simple, they require time consuming training on a per-application basis before they can model the performance with reasonable accuracy. The requirement for training fundamentally limits these models from being applied on-line.

## Chapter 3

## **Analytical Performance Modeling**

Efficient resource demand identification requires fast feedback of the performance under different resource allocations. To meet this requirement, this dissertation employs an analytical model to estimate the application's performance in the searching process of resource demands. Compared with regression models or machine learning models, the analytical model is simple and does not require any training, hence it is a good candidate for resource demand identification. This chapter explains the details of the basic and the extended analytical performance model that will be used in the following chapters for resource demand analysis, heterogeneity-aware application scheduling, and dynamic resource management.

## 3.1 Basic Analytical Model

The analytical performance model is based on the previously proposed interval analysis [12][19], which treats the exhibited Cycle-Per-Instruction (CPI) rate as a sustained steady state execution rate intermittently disrupted by long-latency miss events, such as, L2 cache misses and branch misprediction, etc. With the interval analysis, the total CPI of an application can be treated as the sum of three CPI components [30]:  $CPI_{total} = CPI_{exe} + CPI_{mem} + CPI_{other}$ .

$CPI_{exe}$  represents the steady-state execution rate when the execution is free from any miss events. It is fundamentally constrained by the Instruction Level Parallelism (ILP) of the application and the issue width of the processor. The ILP of the application is typically characterized by the critical dependency chain of the instructions in the instruction window (equivalent to reorder buffer in this dissertation). Assume an instruction window size w, and average critical dependency chain length  $l_w$ . On an idealized machine with unit execution latency,  $l_w$  indicates the average number of cycles required to execute the instructions in the instruction window, hence the average throughput is  $w/l_w$ . For a more realistic machine with non-unit execution latency, this number should be further divided by the average execution latency  $lat_{avg}$  according to Little's law [12]. Therefore, the average ILP,  $\alpha_{avg}$ , can be obtained by  $w/(lat_{avg} \cdot l_w)$ , which also represents the steady-state execution rate if the instruction issue width is unlimited. However, for a realistic processor with limited issue width  $\beta$ , the steady-state execution rate would be saturated at either the average ILP or the issue width, whichever is smaller. As a result,  $CPI_{exe}$  can be obtained by  $1/min(\alpha_{avg}, \beta)$ .

$CPI_{mem}$  represents the penalty caused by the load misses in the last level cache (L2 cache in this paper). It can be calculated by the multiplication between the number of L2 load misses  $N_{L2}$ , and the average memory access latency  $lat_{mem}$ , assuming there are no multiple L2 cache misses outstanding. In practice, in order to hide the load miss latency, L2 caches are usually non-blocking and multiple L2 cache load misses could be outstanding. Under these circumstances, it has been proven that the average load miss latency is reduced to  $lat_{mem}/m_{ovp}$  [12], where  $m_{ovp}$  is the average number of outstanding load misses. Therefore,  $CPI_{mem}$  can be calculated by  $lat_{mem} \cdot N_{L2}/(m_{ovp} \cdot N_{inst})$ , where  $N_{inst}$  is the total number of retired instructions. Note that the term  $N_{L2}/m_{ovp}$  could also be treated as the number of L2 load misses that are not overlapping with each other, and hence is referred to as

the non-overlapped L2 load misses  $N_{novp}$ .

$$CPI_{total} = \frac{1}{min(\alpha_{avg}, \beta)} + \frac{lat_{mem} \cdot N_{novp}}{N_{inst}} + CPI_{other}$$

$CPI_{other}$  is the CPI component caused by other miss events, such as instruction cache misses, branch mispredictions, etc. This dissertation assumes that the resources related with these miss events remain unchanged for different cores. Therefore, this CPI component can be treated as a constant parameter when an application is migrated from one core to anther as long as the application is in stable execution phase. The value of this CPI component can be obtained by transforming equation (1) to  $CPI_{other} = CPI_{total} - CPI_{exe} - CPI_{mem}$ , where  $CPI_{total}$  can be obtained from the performance counter,  $CPI_{ideal}$  and  $CPI_{mem}$  can be derived from the observed program characteristics. The deduced  $CPI_{other}$  can then be plugged into the analytical model to estimate the performance of other cores. Therefore, the basic performance model can be written as follows:

#### 3.2 Extended Performance Model

The basic performance model itself is unable to predict the performance of processor cores with different resource configurations. Specifically, it assumes that each core has a sufficient number of functional units (FUs), the same operating frequency, the same L2 cache sizes, and is executing in single-thread mode. However, when the number of functional units is limited, instructions may be stalled for additional cycles, resulting in lower performance. Similarly, different L2 cache sizes could also influence the number of non-overlapped L2 load misses, and if the core supports Simultaneous Multi-threading (SMT), the co-executing thread(s) could also

influence a thread's performance. Therefore, in order to estimate the performance of different resource allocations, the basic analytical model has to be augmented to capture the performance impact of limited functional units, different operating frequencies, different L2 cache sizes, and the interaction of co-executing threads.

#### 3.2.1 Impact of Limited Functional Units

The limited functional units may stall the instructions for additional cycles, which impacts the performance from two aspects. First, the additional stalled cycles increase the average execution latency, which in turn reduces the observed average ILP. Second, the limited number of functional units may also constrain the number of the instructions that can be issued in one cycle, causing the effective issue width  $\beta_{eff}$  smaller than the nominal one.

To capture these performance impacts, this dissertation presents the ready set size histogram for any given type of FU. The ready set is the set of instructions in the instruction window that are ready for execution on a certain type of functional units, and the ready set size (RSS) is the number of instructions in the ready set, used as an index to the ready set size histogram. Each time a new ready set is encountered, the histogram entry indexed with the corresponding RSS is incremented by one. As shown in Figure 3.1(a), when instruction a finishes execution, instructions b and c are ready to execute. Since both b and c will execute on an Integer ALU (I-ALU), the RSS for I-ALU is 2 and the corresponding entry in the I-ALU RSS histogram is incremented. When instruction b finishes execution, instructions d, e and f are free. Instruction d will execute on load unit; both e and f will execute on the I-ALU, though they have different opcodes. Hence, the new RSS for I-ALU is also 2. Note that even if at this point c is still in ready state, it should not be counted in the new

Figure 3.1: The instruction ready set and the RSS histogram.(a) Example of an instruction dependency graph. (b) I-ALU RSS histogram for SPEC CPU2006 program h264ref.

ready set. Therefore, RSS histogram reflects the inherent property of the workload, and is microarchitecture-independent.

The RSS histogram opens the door to estimate the number of stalled cycles and the effective issue width for any number of FUs. As shown in Figure 3.1(b), the number of I-ALU splits the histogram into two regions. Region A contains instructions with RSS no larger than the I-ALU number, hence instructions in this region would not experience additional stalled cycles caused by I-ALU. While in region B, the I-ALU number is smaller than RSS, causing additional waiting cycles on the ready instructions. Assuming n fully pipelined I-ALU and a ready set with RSS of m, it takes  $\lfloor m/n \rfloor$  additional cycles to finish issuing the instructions in this ready set, contributing an additional cycle-instruction product  $\sum_{i=1}^{\lfloor m/n \rfloor} (m-i \cdot n)$  to the equation of calculating the average instruction latency. Therefore, by considering all the additional stalled cycles caused by a limited number of FUs, the average instruction

latency may be changed significantly, resulting in a modified observed average ILP, which is referred to as  $\alpha'_{avg}$  in this dissertation. On the other hand, instructions in region A and instructions in region B have different observed issue width. While the observed issue width for the instructions in region A equals the physical issue width, the observed issue width for those in region B is limited by the FU number n. Therefore, on average, the effective issue width  $\beta_{eff} = pn + (1-p)\beta$ , where p is the percentage of instructions in region B among the total instructions executed. As a result, with the limited functional units,  $CPI_{exe}$  becomes  $1/min(\alpha'_{avg}, \beta_{eff})$ .

#### 3.2.2 Impact of Operating Frequency

Besides modeling the impact of limited FU numbers, the basic performance model also needs to be augmented to capture the performance impact of different clock frequencies. This could be achieved by converting the CPI to the delay in terms of absolute execution time. Consequently, the extended performance model that considers both operating frequency and limited number of FUs can be written as follows:

$$Delay = CPI_{total} * N_{inst}/f$$

$$= \frac{N_{inst}}{min(\alpha'_{avq}, \beta_{eff}) \cdot f} + t_{mem} \cdot N_{novp} + C_{other}/f$$

where  $N_{inst}$  is the total number of instructions, f is the operating frequency,  $t_{mem}$  represents the absolute memory access time, and  $C_{other}$  refers to the product of  $CPI_{other}$  and  $N_{inst}$ .

#### 3.2.3 Impact of L2 Cache Size

The L2 cache size has direct impact on the number of L2 load misses, which in turn influences the non-overlapped L2 load misses. To estimate the number of L2 load misses, this dissertation employs Mattson's stack distance model [31]. This model exploits the inclusion property of Least Recently Used (LRU) replacement policy (i.e., the content of an N sized cache is a subset of the content of any cache larger than N) and allows us to accurately estimate the number of misses in any fully associative cache. Specifically, this model treats the cache as a large stack organized from Most Recently Used (MRU) position to the LRU position, and each time when a data block is reused, the distance between the position of the block and the MRU position is referred as the stack distance of the block. When a load/store accesses a data block with the stack distance larger than the given cache size, that load/store triggers a cache miss event in a fully associative cache. When it comes to set-associative caches, however, the accuracy of this model slightly decreases mainly because it is unable to capture the conflict misses.

While the block-level stack distance can be profiled off-line, the on-line stack distance profiler is implemented at the cache way level since way partition is more feasible and efficient in terms of implementation cost [25]. As an example, Figure 3.2 shows the stack distance histogram of program *xalancbmk* on an 8-way associative cache, organized from MRU position to LRU position. For caches with its associativity reduced to 6-ways (dash line in the figure), the data with stack distance larger than 6 cannot be hold in the cache, generating cache misses. Therefore, with the stack distance histogram, one can estimate the cache miss rate for any cache ways less than the profiled ways and consequently derive the number of L2 misses.

Figure 3.2: Stack Distance Histogram of SPEC CPU2006 program xalancbmk.

#### 3.2.4 Impact of Memory-Level Parallelism

While the stack distance model is able to estimate the number of misses for a given cache size, it is unaware of Memory-Level Parallelism (MLP), i.e., multiple L2 load misses overlapping with each other. In the basic performance model, the MLP is modeled by using the average number of outstanding load misses  $m_{ovp}$ . However, for a given application, this number can be affected by two factors: the L2 cache size, which determines the total number of L2 load misses; the ROB size, which imposes a "window" on the dynamic instruction stream and controls the amount of exposed MLP. Therefore, to estimate the number of non-overlapped L2 load misses for different ROB sizes and L2 cache sizes, the compounded effect of these two has to be carefully modeled.

Prior research obtains the program's MLP information by simulating caches in detail [12][13]. This dissertation, on the contrary, attempts to decouple MLP modeling from detailed cache simulation, which allows the technique to be applied not

only in off-line resource demand analysis but also in on-line proactive performance prediction. To do so, the profiler generates the maximum number of loads  $LD_{max}$  in a dependency chain and the total number of loads  $LD_{total}$  in an instruction window. Then,  $LD_{total}/LD_{max}$  indicates the average number of loads that could be overlapped with each other in the instruction window. Assuming that the loads in a dependency chain have the same probability of missing L2 cache with other loads,  $LD_{total}/LD_{max}$  becomes the average number of the overlapped L2 load misses, or the MLP of the program. Meanwhile, the profiler also generates a load trace that contains the stack distance of a load and the dynamic instruction ID of the corresponding load, as shown in Figure 3.3(a). The MLP analyzer then walks through the trace, counts the number of L2 load misses that could happen in the instruction window for the given L2 cache size, and calculates the number of non-overlapped L2 misses by dividing the miss number with MLP. The total number of the non-overlapped L2 misses of the program is the sum of the non-overlapped misses in each instruction window:

$$N_{novp}(W,C) = \sum_{i} \left[ \frac{miss\_num(W,C)}{MLP} \right]_{i}$$

(3.1)

where " $\lceil$ " is the ceiling function,  $miss\_num(W, C)$  is the number of L2 misses for the instruction window W and L2 cache size C. Figure 3.3(b) shows the accuracy of this model in estimating the number of non-overlapped L2 misses. The average error between the modeled number of non-overlapped misses and the simulated one is 9.3%, which is reasonably accurate for performance trend modeling.

#### 3.2.5 Impact of Co-executing Threads

The basic performance model only captures the performance of a thread when it is executed alone on the processor core and is free to access all available intra-

Figure 3.3: MLP modeling. (a) The estimation of non-overlapped L2 misses in the presence of MLP. (b) The accuracy of the estimated non-overlapped L2 misses. The results are based on the simulation of the 22 benchmark programs.

core resources. However, when multiple threads simultaneously execute on a core, these threads will compete each other for the shared intra-core resources, causing interference on the performance of each co-executing thread. In practice, to achieve controllable performance for each thread, the shared intra-core resources are dynamically partitioned among the threads [21] except for the issue/dispatch width, which often remains as shared such that one thread can exploit the full execution bandwidth when the other thread is waiting for its miss events to be served [32]. Under this circumstance, the effective issue width of each thread would be significantly different from the physical issue width, and the basic performance model needs to be augmented accordingly.

Assuming a processor with 2-way SMT and per-thread retirement capability, the effective execution rate of the thread can be estimated by analyzing the ILP of the co-executing threads. For example, if the ILP of thread  $T_0$  (referred to as  $\alpha_{T0}$ )

and the ILP of thread  $T_1$  (referred to as  $\alpha_{T1}$ ) are both larger than the issue width  $\beta$  of the processor core, on average each thread can execute at a rate equal to half of the issue width. If we could further obtain the fraction of the time that  $T_0$  is serving a long-latency miss event, the effective execution rate of  $T_1$  can be derived by considering the additional execution bandwidth  $T_1$  has during that fraction of time. Similarly, if  $\alpha_{T0}$  and  $\alpha_{T1}$  are both smaller than  $\beta$  but the sum of these two is larger than  $\beta$ , on average the effective issue width of a thread is determined by the occupancy of its ready instructions:  $\alpha_{T0} \cdot \beta/(\alpha_{T0} + \alpha_{T1})$  for  $T_0$  and  $\alpha_{T1} \cdot \beta/(\alpha_{T0} + \alpha_{T1})$  for  $T_1$ . By considering the fraction of the time in serving the long-latency miss events, the effective execution rate can be also derived. Table 3.1 summarizes the calculation of the effective execution rate under different scenarios. These values are used as the background steady-state execution rates of the performance model in the presence of SMT. Note that these estimations are based on the assumption that IQ uses the oldest-first policy to dispatch ready instructions.

Table 3.1: Estimation of Effective Average Execution Rate for 2-Way SMT

| Cases:                                      | Effective Average Execution Rate                                                  |                                                                                   |  |  |  |

|---------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|

| Cases:                                      | Thread 0 $(T_0)$                                                                  | Thread 1 $(T_1)$                                                                  |  |  |  |

| $\alpha_{T0} < \beta, \alpha_{T1} < \beta,$ | Olmo                                                                              | Olma                                                                              |  |  |  |

| $\alpha_{T0} + \alpha_{T1} < \beta$         | $lpha_{T0}$                                                                       | $lpha_{T1}$                                                                       |  |  |  |

| $\alpha_{T0} < \beta, \alpha_{T1} < \beta,$ | $\frac{\alpha_{T0}*\beta}{\alpha_{T0}+\alpha_{T1}}*(1-f_{T1})+\alpha_{T0}*f_{T1}$ | $\frac{\alpha_{T1}*\beta}{\alpha_{T0}+\alpha_{T1}}*(1-f_{T0})+\alpha_{T1}*f_{T0}$ |  |  |  |

| $\alpha_{T0} + \alpha_{T1} > \beta$         | $\alpha_{T0} + \alpha_{T1} + \alpha_{T0} + \alpha_{T0} + \alpha_{T1}$             | $\alpha_{T0} + \alpha_{T1}$ " (1 $JT0$ ) + $\alpha_{T1}$ " $JT0$                  |  |  |  |

| $\alpha_{T0} > \beta, \alpha_{T1} < \beta,$ | $\frac{\alpha_{T0}*\beta}{\alpha_{T0}+\alpha_{T1}}*(1-f_{T1})+\beta*f_{T1}$       | $\frac{\alpha_{T1}*\beta}{\alpha_{T0}+\alpha_{T1}}*(1-f_{T0})+\alpha_{T1}*f_{T0}$ |  |  |  |

| $\alpha_{T0} + \alpha_{T1} < 2\beta$        | $\alpha_{T0} + \alpha_{T1}$ (1 J11) + $\beta$ + J11                               | $\alpha_{T0} + \alpha_{T1}$                                                       |  |  |  |

| $\alpha_{T0} > \beta, \alpha_{T1} < \beta,$ | $\frac{2*\beta - \alpha_{T1}}{2.0} * (1 - f_{T1}) + \beta * f_{T1}$               | $\frac{\alpha_{T1}}{2.0} * (1 - f_{T0}) + \alpha_{T1} * f_{T0}$                   |  |  |  |

| $\alpha_{T0} + \alpha_{T1} > 2\beta$        | $2.0$ $(1 J11) + p \cdot J11$                                                     | 2.0 * (1                                                                          |  |  |  |

| $\alpha_{T0} < \beta, \alpha_{T1} > \beta,$ | $\frac{\alpha_{T0}*\beta}{\alpha_{T0}+\alpha_{T1}}*(1-f_{T1})+\alpha_{T0}*f_{T1}$ | $\frac{\alpha_{T1}*\beta}{\alpha_{T0}+\alpha_{T1}}*(1-f_{T0})+\beta*f_{T0}$       |  |  |  |

| $\alpha_{T0} + \alpha_{T1} < 2\beta$        | $\alpha_{T0} + \alpha_{T1}$ (2 J11) + $\omega_{T0}$ · J11                         | $\alpha_{T0} + \alpha_{T1}$                                                       |  |  |  |

| $\alpha_{T0} < \beta, \alpha_{T1} > \beta,$ | $\frac{\alpha_{T0}}{20} * (1 - f_{T1}) + \beta * f_{T1}$                          | $\frac{2*\beta - \alpha_{T0}}{2.0} * (1 - f_{T0}) + \beta * f_{T0}$               |  |  |  |

| $\alpha_{T0} + \alpha_{T1} > 2\beta$        | 2.0                                                                               |                                                                                   |  |  |  |

| $\alpha_{T0} > \beta,  \alpha_{T1} > \beta$ | $\frac{\beta}{2.0} * (1 - f_{T1}) + \beta * f_{T1}$                               | $\frac{\beta}{2.0} * (1 - f_{T0}) + \beta * f_{T0}$                               |  |  |  |

## 3.3 Summary

This chapter presents the details of the proposed analytical performance model that will be used in the following chapters. Compared with the existing performance models, the proposed model is decoupled from detailed cache simulations, yet is still able to capture the performance impact of different L2 cache sizes, a key capability that allows this model to be applied in efficient resource demand analysis and performance prediction. The proposed performance model is also able to capture the performance under different functional unit numbers, paving the way for proactive application scheduling in heterogeneous multi-cores with faulty FUs. Overall, the proposed performance model serves as the foundation for resource demand analysis, heterogeneity-aware application scheduling as well as dynamic resource management in SHMPs.

# Chapter 4

# **Experiment Methodology**

The previous chapter described the analytical performance model which is used as the common foundation of resource demand analysis, program-core mapping, application scheduling in static SHMP, and resource management in dynamic SHMP. Before going to the details of each of these techniques, this chapter summaries the simulation platforms, workloads, and metrics that are employed to evaluate the effectiveness and quality of these techniques.

## 4.1 Simulation Platform

#### 4.1.1 Simulation Platform for Resource Demand Analysis

The simulation platform for resource demand analysis is built on top of Sim-Profile from Simplescalar tool set [33]. SimProfile is extensively modified to support the profiling of the statistics of the program characteristics needed by the performance model. The framework of resource demand analysis is evaluated on an out-of-order superscalar processor with two-level cache subsystem. The configuration ranges of relevant resources are listed in Table 4.1. Note that the associativity and the cache block size are kept constant across all possible L2 cache sizes as these aspects are not explored in this dissertation. The number of execution units is chosen such that the overall configuration is balanced. In total, the listed configurations cover over 100K design nodes. When evaluating the estimation of single-resource

demand, it is required that other resource configurations are fixed. However, due to the large design space, it is impossible for us to evaluate our framework exhaustively across all configurations. Therefore, this work uses three representative configuration sets: config-S(mall), config-M(edium), and config-L(arge), as the base configurations to evaluate our resource estimation model. The details of these configuration sets are also shown in Table 4.1.

Table 4.1: Configuration Options

| Items          | Configuration Options  | config-S           | config-M | config-L |

|----------------|------------------------|--------------------|----------|----------|

| Issue Width    | 1 :: 2x :: 8           | 1                  | 4        | 8        |

| ROB size       | 16 :: 2x :: 512        | 16                 | 128      | 512      |

|                | 64KB::2x::2048KB       | 64KB               | 512KB    | 2048KB   |

| L2 D-Cache     | 8-way associative      | 8-way              | 8-way    | 8-way    |

|                | 64B                    | 64B                | 64B      | 64B      |

|                | 32KB                   | 32KB               | 32KB     | 32KB     |

| L1 I-cache     | 2-way                  | 2-way              | 2-way    | 2-way    |

|                | 64B                    | 64B                | 64B      | 64B      |

|                | 32KB                   | 32KB               | 32KB     | 32KB     |

| L1 D-cache     | 4-way                  | 4-way              | 4-way    | 4-way    |

|                | 64B                    | 64B                | 64B      | 64B      |

| Branch         | 1st-level: 8::2x::1K   | 1024               | 1024     | 1024     |

| Predictor(PAg) | 2nd-level: 128::2x::4K | 4096               | 4096     | 4096     |

| Clock Freq.    | 0.5::0.1::2 (GHz)      | $0.5~\mathrm{GHz}$ | 1 GHz    | 2 GHz    |

For the evaluation of the resource demand analysis framework, this dissertation assumes the memory access latency to be 200ns, or 200 cycles at a clock frequency of 1 GHz. This latency number in terms of cycles scales proportionally with the operating frequency. The hit latencies of L1 and L2 caches are calibrated against Cacti 5.0 [34] under 90nm technology. The latencies of other execution units are also scaled to 90nm technology. The branch misprediction penalty is set to 20 cycles at 1 GHz. The power data of the interested processor configurations is collected using Wattch [35].

#### 4.1.2 Simulation Platform for Program-core Mapping

The proposed framework for program-core mapping is evaluated on a hypothetical single-ISA heterogeneous quad-core processor. The detailed configurations of these cores are listed in Table 4.2. Each core is an out-of-order processor, and has a private 512K L2 cache with a hit latency of 12 cycles, and a miss latency of 200 cycles. Other parameters not shown in the table are chosen in a way that the design of the core is balanced. Since this work focuses on establishing the mapping relationship between programs and cores, the workloads are chosen to be independent with each other and the core-level communication is not considered in the evaluation of this part of the work. Note that the core-level communication (e.g., cache snooping) are symmetrical and tend to impose similar impact on the independent workloads, therefore, this simplifying assumption would not affect the validity of the evaluation.

Table 4.2: Configurations of Each Core

| ITEMS  | Configuration                                        |

|--------|------------------------------------------------------|

|        | Out-of-order, single-issue, 1K Gshare, 32KB 4-way    |

| Core 1 | L1 d-cache 64byte, 4k 2-way i-cache 64byte, 512k L2  |

|        | cache, L2 access latency 12 cycles                   |

|        | Out-of-order, 2-issue, 2K Gshare, 64KB 4-way         |

| Core 2 | L1 d-cache 64byte, 8k 2-way i-cache 64byte, 512k L2  |

|        | cache, L2 access latency 12 cycles                   |

|        | Out-of-order, 4-issue, 4K Ghsare, 64 KB 4-way        |

| Core 3 | L1 d-cache 64byte, 16k 2-way i-cache 64byte, 512k L2 |

|        | cache, L2 access latency 12 cycles                   |

|        | Out-of-order, 8-issue, 8K Gshare, 128 KB 4-way       |

| Core 4 | L1 d-cache 64byte, 16k 2-way i-cache 64byte, 512k L2 |

|        | cache, L2 access latency 12 cycles                   |

Similar with the evaluation of resource demand analysis, the program-core mapping framework also uses SimProfile from Simplescalar tool set [33] to profile programs and collect the needed program characteristics, including instruction de-

pendence distribution, stack distance distribution. Again, Wattch [35] is employed to obtain the performance and power data for each benchmark program.

#### 4.1.3 Simulation Platform for Application Scheduling in Static SHMP

The application scheduling in static SHMP is evaluated on a quad-core SPARCv9 OpenSolaris system modeled by a full system simulator Simics [36], extended with the GEMS toolset [37]. Each core in the CMP is 4-issue out-of-order processor modeled by Opal [37]. The simulated CMP system also contains a detailed memory subsystem model, which includes an inter-core last-level cache network and a detailed memory controller. In addition, the simulated system supports software data prefetching. Table 4.3 lists the nominal configurations of the CMP system in detail. The dynamic power of the processor cores is estimated by Wattch [35], and the leakage power on caches and other SRAM structures in the core is estimated by Cacti 5 [34]. The simulator also uses Orion [38] to estimate the power on the interconnection network of the last-level cache. Therefore, the performance and power overhead of application migration is fully modeled.

This work focuses on the core-level heterogeneity on frequency, Integer ALU (I-ALU) number and L2 cache size, yet it is infeasible to evaluate every possible configuration. Therefore, this dissertation evaluates three sets of heterogeneous configurations created by varying these resources over their nominal values, as shown in Table 4.4. These configuration sets are organized as low heterogeneity (LH) where only frequency varies, medium heterogeneity (MH) where both frequency and I-ALU number vary, and high heterogeneity (HH) where all three resources vary. While there are other heterogeneous configurations, these three configuration sets cover the representative degrees of heterogeneity caused by manufacturing imperfection.

Table 4.3: Nominal Configurations of the CMP system

|        | Parameter                     | Configurations                             |

|--------|-------------------------------|--------------------------------------------|

|        | Clock Frequency               | 4GHz                                       |

|        | Fetch/Issue/Commit Width      | 4/4/4                                      |

|        | Ld/St Units                   | 2/2                                        |

| Core   | I-ALU/FP Units/FP Multipliers | 4/2/2 (fused multiply/add for I-ALU)       |

|        | ROB size                      | 128                                        |

|        | Load/Store Queue Size         | 32/32                                      |

|        | Branch Predictor              | YAGS, 16 PHT bits, 10 Tag bits             |

|        | L1 I-Cache/D-Cache            | 32KB, 2-way, 64Byte, LRU, 1-cycle          |

| Cache  | L2 Cache                      | 2MB per core, 8-way, 64Byte, LRU, 12-cycle |

| Cache  | L2 MSHR Entry                 | 32                                         |

|        | Coherence Protocol            | Directory-based MOESI                      |

|        | Size/Model                    | 4GB/DDR2-800                               |

| Memory | Controller                    | FR-FCFS policy [39]                        |

|        | Organization                  | 8 banks per rank, 2 ranks per DIMM         |

Table 4.4: Configurations of the CMP system

|            | Configurations |     |     |               |     |     |             |     |     |      |     |      |

|------------|----------------|-----|-----|---------------|-----|-----|-------------|-----|-----|------|-----|------|

| Parameter  | Low Heter.     |     |     | Medium Heter. |     |     | High Heter. |     |     |      |     |      |

|            | C-0            | C-1 | C-2 | C-3           | C-0 | C-1 | C-2         | C-3 | C-0 | C-1  | C-2 | C-3  |

| Freq.(GHz) | 4              | 3.6 | 3.2 | 2.8           | 4   | 3.6 | 3.2         | 2.8 | 4   | 3.6  | 3.2 | 2.8  |

| I-ALU      | 4              | 4   | 4   | 4             | 4   | 2   | 3           | 1   | 4   | 2    | 3   | 1    |

| L2 Cache   | 2,             | 2,  | 2,  | 2,            | 2,  | 2,  | 2,          | 2,  | 2,  | 1.5, | 1,  | 0.5, |

| (MB, Ways) | 8              | 8   | 8   | 8             | 8   | 8   | 8           | 8   | 8   | 6    | 4   | 2    |

#### 4.1.4 Simulation Platform for Resource Management in Dynamic SHMP

The resource management in dynamic SHMP is also evaluated on a quadcore SPARCv9 OpenSolaris system modeled by a full system simulator Simics [36], extended with the GEMS toolset [37]. Each core in the CMP is a 4-issue out-of-order processor and supports 2-way SMT with ICOUNT [23] fetch policy. The simulated CMP system also contains a detailed memory subsystem model, which includes an inter-core last-level cache network and a detailed memory controller. Table 4.5 lists the configurations of the CMP system in detail. Again, the dynamic power of the processor cores is estimated by Wattch [35], and the leakage power on caches and other SRAM structures in the core is estimated by Cacti 5 [34]. Orion [38] is used to estimate the power on the interconnection network of last level caches.

The ROB size is partitioned at the granularity of 32 entries. Other intra-core resources such as issue queue size and physical register number are partitioned in proportion to the ROB size. Each thread is guaranteed to have at least 32 entries of ROB size. The L2 cache is shared among the threads, and its size is partitioned at the granularity of cache ways, with each thread allocated with at least one cache way. The CMP system supports per-core DVFS, with the frequency of each core ranging from 2GHz to 4GHz at the step of 0.1GHz. This dissertation assumes that the CMP system reaches the power budget when it is fully loaded and each core is running at 3GHz.

Table 4.5: Configurations of the CMP system

|        | Parameter                     | Configurations                       |

|--------|-------------------------------|--------------------------------------|

|        | Maximum Clock Frequency       | 4GHz                                 |

| Como   | Fetch/Issue/Commit Width      | 4/4/4                                |

| Core   | Ld/St Units                   | 2/2                                  |

|        | I-ALU/FP Units/FP Multipliers | 4/4/2 (fused multiply/add for I-ALU) |

|        | ROB size/Issue Queue          | 256/160                              |

|        | Load/Store Queue Size         | 64/64                                |

|        | Branch Predictor              | YAGS, 16 PHT bits, 10 Tag bits       |

|        | Physical Register Number      | 380                                  |

|        | L1 I-Cache/D-Cache            | 32KB, 2-way, 64Byte, LRU, 1-cycle    |

| Cache  | L2 Cache                      | 16MB, 32-way, 64Byte, LRU, 12-cycle  |

| Cache  | L2 MSHR Entry                 | 32                                   |

|        | Coherence Protocol            | Directory-based MOESI                |

|        | Size/Model                    | 4GB/DDR2-800                         |

| Memory | Controller                    | PAR-BS policy [40]                   |

| Memory | Organization                  | 8 banks per rank, 2 ranks per DIMM   |

#### 4.2 Workloads

#### 4.2.1 Workloads for Program Resource Demand Analysis

The workload to evaluate the framework of resource demand analysis is composed of 22 SPEC CPU2006 programs [41] (gamess, dealII, calculix, povray, tonto, lbm,wrf are not included in the workload as they fail to compile to Alpha ISA). Each of the 22 programs is compiled to Alpha-ISA with peak configurations. To speedup the evaluation, the single Simpoint interval with 100 million instructions [42] is used to represent each program.

#### 4.2.2 Workloads for Program-core Mapping