Copyright

by

Byeong Kil Lee

2005

### The Dissertation Committee for Byeong Kil Lee Certifies that this is the approved version of the following dissertation:

## Network Processor Design: Benchmarks and Architectural Alternatives

| Committee:                |

|---------------------------|

| Lizy K. John, Supervisor  |

| Ronald Barr               |

| Chen-Chau Chu             |

| Sanjay Shakkottai         |

| Earl E. Swartzlander, Jr. |

## Network Processor Design: Benchmarks and Architectural Alternatives

by

Byeong Kil Lee, B.S.E, M.S.E.

#### **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

August 2005

### Acknowledgements

I would like to thank my advisor, Dr. Lizy John for her advice, guidance, and support. She has had a significant influence not only as my graduate advisor but also on my life. Her professional integrity and pursuit of perfection helped me become a better individual. Her thoughtfulness and understanding the status of international students made me have more freedom towards research without any financial problem. I am grateful to her for unconditional support and encouragement she gave me throughout my Ph. D. study. I'm also grateful to her guiding me to have great experiences on professional activities.

I also thank my committee, Prof. Ronald Barr, Dr. Chen-Chau Chu, Prof. Sanjay Shakkottai, and Prof. Earl E. Swartzlander Jr. for their invaluable comments, productive suggestions, and the time to reading my thesis.

I would like to thank the students (past and current) at the Laboratory for Computer Architecture (LCA) - Deepu Talla, Ravi Bhargava, Juan Rubio, Madhavi Valluri, Tao Li, Rob Bell, Yue Luo, Shiwen Hu, Anand Rajan, Aashish Phansalkar, Ajay Joshi, Sean Leather, Lloyd Bircher, Hari Angepat, Jason Matalka and Hareesh Pottamsetty. They have contributed to my research by providing valuable comments on drafts of my paper submissions and useful feedback at practice talks.

I would like to thank Dr. Thang Tran, Teik Tan, Ty Garibay and Dr. Jim Bondi for providing me with an opportunity to work at Texas Instruments, Austin. I also thank all team members – Bhasi, Sam, James, Abraham, Paul, Sree, Jeff, Arjun, Murali, Rajinder, Rao, Bob, Hongjoong and Bill.

Thanks to Linda, Shirley, Debi, Melanie, Amy and other administrative assistants who worked in Computer Engineering in the past years.

Finally, I would like to thank my parents, wife, Jisop (son), Hayoung (daughter) and friends who have had a tremendous influence on my life.

**BYEONG KIL LEE**

The University of Texas at Austin

August 2005

**Network Processor Design: Benchmarks and**

**Architectural Alternatives**

Publication No.

Byeong Kil Lee, Ph. D.

The University of Texas at Austin, 2005

Supervisor: Lizy John

The last decade saw phenomenal growth in information technology and network

communication. The network interfaces also have to keep up with the speed, throughput

and capability to support all the workloads. Network processors (NPs) have recently been

introduced in the network interfaces to process complex workloads.

This dissertation investigates architectural alternatives for network processors.

The network processor should be able to process modern network workloads without

slowing down line speed. In order to handle variety of emerging applications, good un-

derstanding of the target application from the architectural perspectives is essential.

While most of the previous research and commercial products for NPs are dedicated to

routing and communication related to data-plane applications, control-plane applications

where congestion control and QoS issues are dealt with are not well understood. With the

vii

demands of emerging network applications, it is imperative to develop and quantitatively characterize the NP control plane workloads to guide architects for designing future NPs.

In this dissertation, a new benchmark suite, called *NpBench*, is proposed for network processors and its architectural workload characteristics are studied. The NpBench suite includes 5 control plane applications and 5 data plane applications. The NpBench suite is implemented using C and is opened to public. Large number of institutions in the world has licensed and several papers and articles cite the NpBench. The NpBench suite fills a major void that exists in the evaluation and benchmarks of NPs.

Another major contribution of this dissertation is architectural enhancements for network processing. First the parallelism characteristics of network processing applications were investigated to see the possibility of identifying it statically. Based on the investigation, it is found that the success of VLIW in the multimedia field can be applied to the network processor domain as a processing element for a parallel architectural implementation.

As alternative solutions of existing network processor architectures, hardware acceleration techniques are proposed to deal with new emerging workloads. Also, the feasibility of extracting common ISA extensions over variety of network workloads is investigated for accelerating the capability of a processing element within a parallel architecture.

## **Table of Contents**

| List of Tables                                                                     | xii  |

|------------------------------------------------------------------------------------|------|

| List of Figures                                                                    | xiii |

| Chapter 1: Introduction                                                            | 1    |

| 1.1 Network Processor Architectures                                                | 1    |

| 1.2 Network Processor Workloads                                                    | 4    |

| 1.3 The Problem                                                                    | 6    |

| 1.4 Objectives                                                                     | 7    |

| 1.5 Thesis Statement                                                               | 10   |

| 1.6 Contributions                                                                  | 10   |

| 1.7 Organization                                                                   | 14   |

| Chapter 2: Related Work                                                            | 16   |

| 2.1 Network Processor Benchmarks                                                   | 16   |

| 2.2 Architectural Characteristics of Network Processor Applications                | 17   |

| 2.3 Network Processor Architectures                                                | 18   |

| Chapter 3: Development and Characterization of a Network Processor Benchmark Suite | 21   |

| 3.1 Investigation of Modern Network Workloads                                      | 21   |

| 3.2 Description of the Applications in the NpBench Suite                           | 28   |

| 3.2.1 Traffic-management and QoS Group (TQG) Benchmarks                            | 28   |

| 3.2.2 Security and Media processing Group (SMG) Benchmarks                         | 32   |

| 3.2.3 Packet Processing Group (PPG) Benchmarks                                     | 35   |

| 3.3 Implementation                                                                 | 36   |

| 3.4 Architectural characteristics of NpBench Workloads                             | 37   |

| 3.4.1 Experimental Methodology                                                     | 37   |

| 3.4.2 Instruction Distribution                                                     |      |

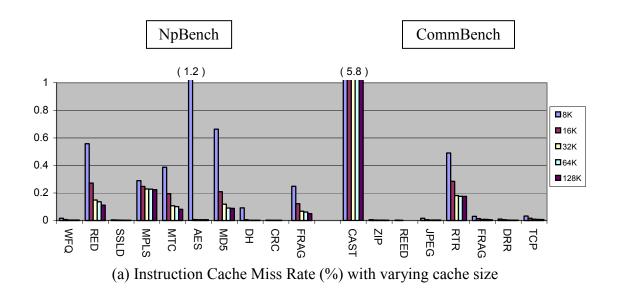

| 3.4.3 Cache Behavior                                                               | 40   |

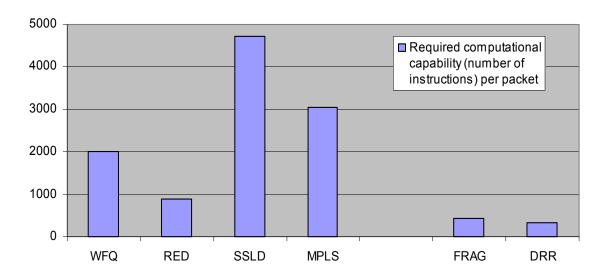

| 3.4.4 Available Instruction Level Parallelism                                      | 42   |

| 3.4.5 Required Computation Capability per Packet                                                          | 42 |

|-----------------------------------------------------------------------------------------------------------|----|

| 3.5 Architectural Implications                                                                            | 45 |

| 3.6 Summary                                                                                               | 47 |

| Chapter 4: Bottlenecks in Network Processor Applications                                                  | 48 |

| 4.1 Experimental Methodology                                                                              | 48 |

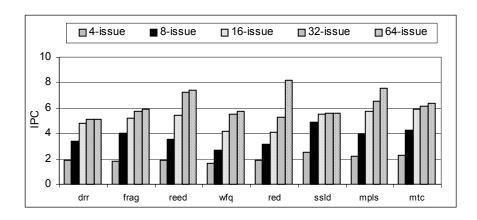

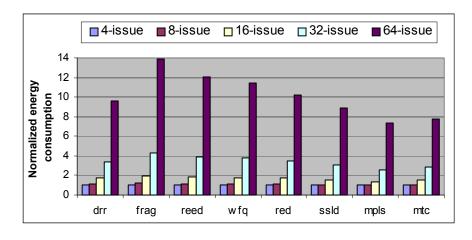

| 4.2 Effectiveness of Wide Issue Processors                                                                | 50 |

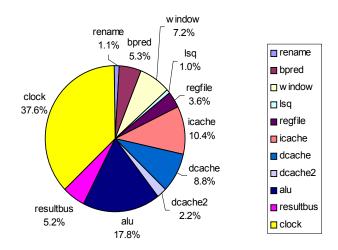

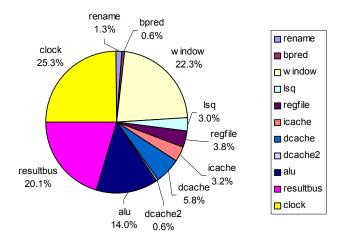

| 4.3 Power Consumption of Wide Issue Superscalars                                                          | 51 |

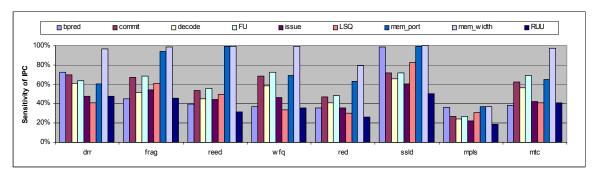

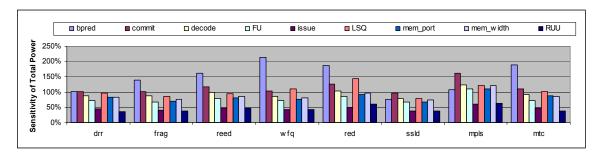

| 4.4 Sensitivity Analysis                                                                                  | 53 |

| 4.5 Summary                                                                                               | 57 |

| Chapter 5: Architecture with Statically Identified Parallelism                                            | 59 |

| 5.1 Background                                                                                            | 59 |

| 5.2 Workloads                                                                                             | 62 |

| 5.3 Experimental Framework                                                                                | 64 |

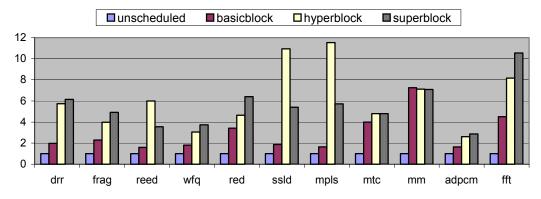

| 5.4 Performance and Power Characteristics of NP and Multimedia Workloads on Static Scheduled Architecture | 66 |

| 5.4.1 Performance Metric in VLIW                                                                          | 66 |

| 5.4.2 Performance Characteristics                                                                         | 67 |

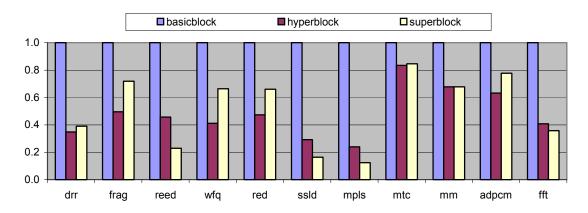

| 5.4.3 Power Characteristics of NP and Multimedia Workloads on VLIW                                        | 70 |

| 5.4.4 Required Parallelism for NP Workloads                                                               | 71 |

| 5.5 Summary                                                                                               | 72 |

| Chapter 6: Hardware Acceleration Techniques for Control-plane Workloads in Network Processors             | 74 |

| 6.1 Hardware Acceleration for Congestion Control Applications                                             | 74 |

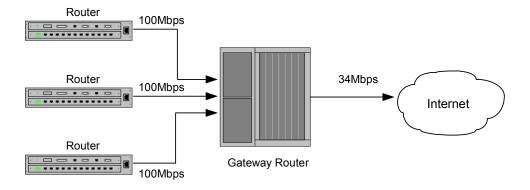

| 6.1.1 Motivation                                                                                          | 75 |

| 6.1.2 Workload Characterization                                                                           | 78 |

| 6.1.2.1 Experimental framework                                                                            | 78 |

| 6.1.2.2 Kernel Characteristics                                                                            | 79 |

| 6.1.2.3 Bottleneck Analysis                                                                               | 80 |

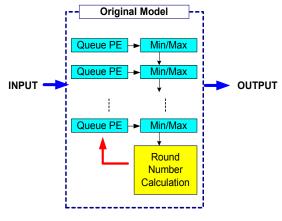

| 6.1.3 Acceleration Model                                                                                  | 80 |

| 6.1.4 Experimental Results and Performance Evaluation                                                     | 85 |

| 6.2 Hardware Acceleration for Media Transcoding Applications                                              | 87 |

| 6.2.1 Motivation                                                                           | 87  |

|--------------------------------------------------------------------------------------------|-----|

| 6.2.2 Workload Characterization                                                            | 88  |

| 6.2.2.1 Experimental Framework                                                             | 89  |

| 6.2.2.2 Kernel Characteristics                                                             | 89  |

| 6.2.2.3 Bottleneck Analysis                                                                | 90  |

| 6.2.3 Acceleration Model                                                                   | 90  |

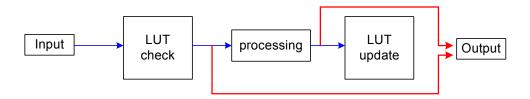

| 6.2.4 Experimental Results and Performance Evaluation                                      | 93  |

| 6.3 Hardware Acceleration for LUT-related Applications                                     | 95  |

| 6.3.1 Motivation                                                                           | 95  |

| 6.3.2 Workload Characterization                                                            | 96  |

| 6.3.2.1 Experimental Framework                                                             | 97  |

| 6.3.2.2 Kernel Characteristics                                                             | 97  |

| 6.3.2.3 Bottleneck analysis                                                                | 98  |

| 6.3.3 Acceleration Model                                                                   | 98  |

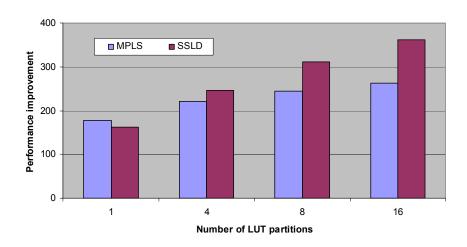

| 6.3.4 Experimental Results and Performance Evaluation                                      | 100 |

| 6.4 Summary                                                                                | 102 |

| Chapter 7: Instruction Set Extensions for Efficient Network Processing                     | 105 |

| 7.1 Motivation                                                                             | 105 |

| 7.2 Instruction set extensions for congestion control applications                         | 106 |

| 7.3 Performance analysis of new instruction extensions for congestion control applications | 108 |

| 7.4 Summary                                                                                | 109 |

| Chapter 8: Conclusions and Future Work                                                     | 111 |

| 8.1 Conclusions                                                                            |     |

| 8.2 Future Work                                                                            |     |

| Bibliography                                                                               | 119 |

|                                                                                            |     |

| VITA                                                                                       | 135 |

## **List of Tables**

| Table 1.1 Required parallelism for control plane workloads                        | 7   |

|-----------------------------------------------------------------------------------|-----|

| Table 3.1 Functional grouping of network processor workloads                      | 23  |

| Table 3.2 Benchmarks in the NpBench suite                                         | 27  |

| Table 3.3 Instruction distribution                                                | 39  |

| Table 3.4 Processing capability of single processor according to line rates and   |     |

| required processing capability of benchmarks                                      | 45  |

| Table 4.1 Architectural configurations for the experiments                        | 49  |

| Table 4.2 Selected workloads: 8 NP applications and 3 multimedia kernels          | 49  |

| Table 4.3 Impact of resource constraints on energy distribution (WFQ)             | 56  |

| Table 5.1 Selected workloads: 8 NP applications and 3 multimedia kernels          | 63  |

| Table 5.2 Architectural configurations for the VLIW experiments                   | 66  |

| Table 5.3 Performance characteristics for selected NP applications and multimedia |     |

| kernels on VLIW                                                                   | 68  |

| Table 5.4 Static code size of different region formation techniques               | 69  |

| Table 5.5 Required parallelism for NP workloads                                   | 72  |

| Table 6.1 Required parallelism for congestion control workloads                   | 77  |

| Table 6.2 Instruction distribution of congestion control applications and crypto  |     |

| applications                                                                      | 79  |

| Table 6.3 Instruction distribution of media transcoding applications              | 90  |

| Table 6.4 Instruction distribution of MPLS and SSLD applications                  | 97  |

| Table 7.1 A extensions for congestion control applications                        | 107 |

| Table 7.2 Architectural configurations for performance analysis                   | 109 |

## **List of Figures**

| Figure 1.1 Network processors                                                         | 4  |

|---------------------------------------------------------------------------------------|----|

| Figure 2.1 Overall architecture of NP                                                 | 19 |

| Figure 3.1 WFQ (Weighted Fair Queuing)                                                | 29 |

| Figure 3.2 RED (Random Early Detection)                                               | 30 |

| Figure 3.3 SSLD (SSL Dispatcher)                                                      | 31 |

| Figure 3.4 MPLS (Multi Protocol Label Switching)                                      | 32 |

| Figure 3.5 MTC (Media Transcoding)                                                    | 34 |

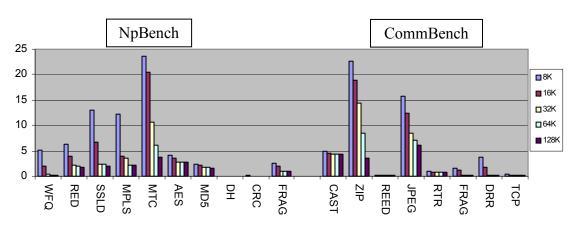

| Figure 3.6 Cache performance of network processor benchmarks                          | 41 |

| Figure 3.7 Available parallelism with ten function units                              | 43 |

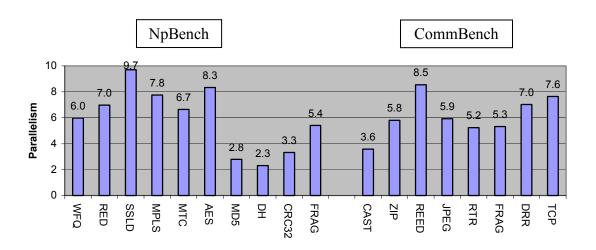

| Figure 3.8 Required computational capability (in terms of number of instructions) per |    |

| packet                                                                                | 44 |

| Figure 4.1 Performance impact of wide issue in NP applications                        | 50 |

| Figure 4.2 Energy consumption of wide issue Superscalar architectures for NP          |    |

| applications                                                                          | 51 |

| Figure 4.3 Power distribution in dynamic execution of NP applications                 | 52 |

| Figure 4.4 Sensitivity analysis with respect to the resource constraints in NP        |    |

| applications                                                                          | 54 |

| Figure 5.1 Conceptual structure of parallel architecture for network processors       | 62 |

| Figure 5.2 Main flow of the WFQ application.                                          | 64 |

| Figure 5.3 Data flow of NP and multimedia workloads                                   | 65 |

| Figure 5.4 Performance characteristic on VLIW                                         | 69 |

| Figure 5.5 Power consumption on VLIW                                                  | 71 |

| Figure 6.1 Router system                                                              | 76 |

| Figure 6.2 Hardware acceleration model for WFQ                                  |     |

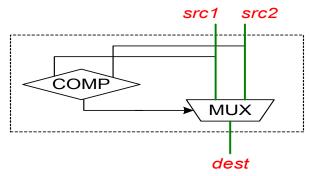

|---------------------------------------------------------------------------------|-----|

| Figure 6.3 Hardware acceleration model for RED                                  | 84  |

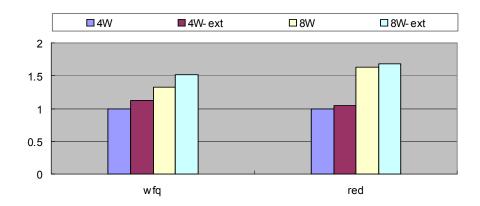

| Figure 6.4 Performance evaluation of hardware acceleration model for congestion |     |

| control applications                                                            | 86  |

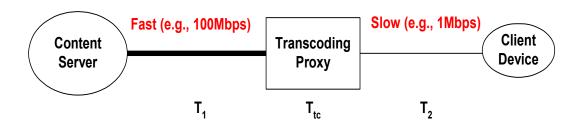

| Figure 6.5 Media transcoding                                                    | 88  |

| Figure 6.6 Hardware acceleration model for media transcoding                    | 92  |

| Figure 6.7 Performance evaluation of hardware acceleration model (media         |     |

| transcoding)                                                                    | 94  |

| Figure 6.8 Data flow of LUT related applications                                | 96  |

| Figure 6.9 Partitioned LUT [6]                                                  | 99  |

| Figure 6.10 Hardware acceleration model for LUT checking module                 | 101 |

| Figure 6.11 Performance evaluation of hardware acceleration model (LUT related  |     |

| application)                                                                    | 102 |

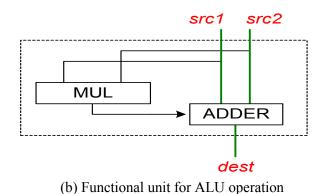

| Figure 7.1 Functional units for new instruction sets                            | 108 |

| Figure 7.2 Performance evaluation of new instruction extensions                 | 110 |

#### **Chapter 1: Introduction**

The last decade saw phenomenal growth in information technology and network communication. As Internet and network technologies have exponentially grown and evolved, the requirement of network interface has become more complex and diverse. Also, various applications and protocols require more intelligent processing over the network. To keep up with these trends of emerging network applications, programmable microprocessors called the network processor (NP) are introduced in network interfaces to handle the demands of modern network applications.

Several vendors are releasing various network processors using different architectural concepts to meet the features of network application workloads. However, existing network processors are designed for packet processing. Modern network workloads include significant control operations in addition to packet routing. Along with rapidly changing network environments and requirements, alternative architectures to handle emerging network applications are required. This chapter describes (1) the necessity for considering emerging workloads in network processor design, and (2) the objectives and contributions of this dissertation.

#### 1.1 NETWORK PROCESSOR ARCHITECTURES

Network processors can be used in various node positions over the network, such as core, edge and access routers. Core routers (10 Gbps rate) are placed in the middle of

the network, so they are critical for performance and least responsive to flexibility. Edge routers are placed in between core and access devices, requiring medium data rate (2.5 Gbps) and a certain amount of flexibility. URL load balancers and firewalls are examples of edge router functions. Access routers (1 Gbps) provide network access to various devices. Most of their works are related to aggregating and forwarding numerous traffic streams through the network [18][19][74][94][103][112].

The conventional applications of network interface mainly consist of packet processing and classification algorithms. However, modern role of such an interface includes congestion control, network security, accounting [38], network address/protocol translations, load balancing and media transcoding. The processing capability of these emerging workloads must be at a level equivalent to the speed of the network. As a solution to this problem, many NP vendors use the concept of packet-level parallelism (PLP) to satisfy high-performance demands of networks. In fact, various companies use parallel architectures such as single chip multiple processor or fine-grain multithreaded processors to meet the packet-level parallelism [70].

In order to extract the parallelism, it is important to understand the attributes of target applications. More importantly, choosing an appropriate benchmark suite is also a significant factor to successfully design and evaluate the processors.

While GPPs (General Purpose Processors) are flexible to rapidly developing network applications and protocols, they do not provide enough performance to process data at wire rates. For example, packet throughput of a 10Gbps link is 19.5 million packets per second, assuming average packet size of bytes [6][45]. Modern network applications require thousands of instructions to be executed per packet in order to accomplish all the

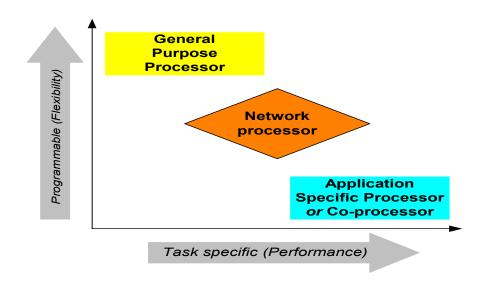

control plane activities required for the packet. General purpose processors at Gigahertz frequencies are not enough to accomplish it. More powerful architectures are required to manage the workloads. Dedicated ASPs (Application Specific Processors) are designed to process packets at wire rates but they are inconvenient when required to add or change the features in order to support new environments. The network processor is a programmable processor or an instruction-set processor specialized for a particular application domain. As shown in Figure 1.1, the network processor exists in the middle range between GPPs and dedicated ASPs.

Due to the variety of application spaces being addressed by network processors, there could be a wide range of NP architectures and implementations. For the enterprise service, several companies developed RISC-based NP with ASIC blocks for networking functions such as IXP 1200/2000 series by Intel [52], CXE-16 by Switchcore, CS2000 by Chameleon etc. For the high-end service, Motorola (C-port) [27], Lucent (FPP/RSP) [71], EZChip (NP-1) [37] and Vitesse/ Sitera(IQ2000) have used network-specific ASICs with the features of network classifying, QoS, etc. Some companies like Chrysalis-ITS, Alliance, NetLogic have developed co-processors with the functions such as routing table, classification or cryptography [96].

Recently, Crowley, *et al.* [28] presented that simultaneous multithreading is best suited for some of the network applications. Recent research and commercial products for network processors show the use of multithreading and vector-type array processing. Melvin, *et al.* [74] utilize multiple multithreaded processing engines to get a high degree of thread-level parallelism (TLP) in an NP design that supports 256 simultaneous threads in eight processing engines. In this scheme, each thread has its own independent register

file, while sharing functional resources and memory ports with other threads. ClearSpeed [24] introduces an MTAP (Multi-Threaded Array Processing) processor, which provides a scalable processing solution, based on an array of 10s to 1,000s of small processing elements. Each PE has its own local memory and I/O capability. Although these implementations can meet the required performance, they have large amounts of hardware and programming complexity, cost and power problems.

Figure 1.1 Network processors

#### 1.2 NETWORK PROCESSOR WORKLOADS

The bottleneck in communication networks is not just due to bandwidth anymore.

Ability to provide flexible processing capability in order to support several emerging ap-

plications and meet their heavy processing workloads is equally important [64]. Major challenges for high bandwidth have reached tremendous advances from optical network approaches, a solution to bandwidth-centric bottleneck – currently 10Gbps (OC-192) at core router exists and 40Gbps (OC-768) is now starting to emerge. In modern network areas, more complex protocols and various network services (e.g., Quality of Service, IPSec, IPv6, etc.) require significant processing power for highly intelligent applications, so the bottleneck of communication network has moved to the network nodes. Accordingly, extracting representative benchmarks from wide range of emerging network applications and characterizing their properties are essential for designing network processors and evaluating their performance.

NP applications can be functionally categorized into two types of operations: data plane operations and control plane operations. The data plane performs packet forwarding, fragmentation and checksum calculation. The control plane handles flow management, signaling, higher-level protocol and other control tasks [3][26][64]. Over the past few years, several vendors have been releasing NPs using a number of different architectures, but most of them are optimized for throughput mostly in data plane. Also, existing benchmark suites for network processors primarily contain data plane workloads, which perform packet processing for a forwarding function. Although NPs have initially been targeted for data plane applications as a conventional workload of NPs, they also play a major role in the control plane. In fact, with the increased demand for complex processing, the boundaries between data plane and control plane have become blurred [1]. Control plane operations have become part of most network processor workloads and the significance of control plane has become greater. The recent trend is that some control plane

activities, such as TCP and SSL applications, are being considered as a commodity. Since there are a lot of control mechanisms in TCP, it cannot be easily converted into an ASIC (Application Specific Integrated Circuit) and it has mostly been left to software solutions. The proliferation of control plane workloads has made it clear that control plane operations should be included in NP benchmarks.

#### 1.3 THE PROBLEM

While most of the previous research and commercial products for NPs are dedicated to data-plane applications, control-plane applications are not well understood. With the demands of these emerging network applications, it is imperative to develop and quantitatively characterize the NP control plane workloads to guide architects for designing future NPs.

The network processor on the physical port of a router should be able to process the modern workloads without slowing down line speed. As shown in Table 1.1, computational load per packet ranges from 880 to 4,800, when assuming a stream of minimum-sized packets of 64 bytes and a single processor of 1 GHz clock frequency. The required parallelism (number of instructions per packet) for executing NP applications is in the range of  $2 \sim 356$  [64]. Hence a conventional processor is not enough to handle these workloads. Relevant research is required to identify appropriate architectures to efficiently execute these emerging workloads [53][69][72][75][87].

Table 1.1 Required parallelism for control plane workloads

| Applications | Computational load per packet | Required parallelism (with a unity ILP 1 GHz processor) |          |          |

|--------------|-------------------------------|---------------------------------------------------------|----------|----------|

|              |                               |                                                         |          |          |

|              | (number of                    | 1Gbps                                                   | 10Gbps   | 40Gbps   |

|              | instructions)                 | (~OC-24)                                                | (OC-192) | (OC-768) |

| MPLS         | 3,051                         | 6                                                       | 60       | 254      |

| SSLD         | 4,727                         | 10                                                      | 94       | 356      |

| WFQ          | 2,005                         | 4                                                       | 40       | 167      |

| RED          | 881                           | 2                                                       | 17       | 74       |

#### 1.4 OBJECTIVES

Recent research and commercial products for parallel implementation of network processors are mostly dedicated to data plane applications with multithreaded and vector-type array processors [24][81]. Although these complex hardware implementations can fulfill the demanded performance using massively parallel architectures, they still have problems related to cost of hardware, power, low utilization ratio of processing elements and hardware complexity. This research focus on the following objectives:

- Create a suite of network processor workloads including control plane, so that

NPs are designed considering a realistic network workload

- Characterize and understand emerging NP workloads to obtain directions for architecture research

- Investigate NP architectural alternatives for emerging network workloads

- Create hardware accelerators for emerging network workloads

The first objective is to fill the gap that exists in the field of network benchmarks. The objective is to study network algorithms and create benchmarks which can be used in architecture research. Modern network applications can be classified into three functional groups: traffic-management and quality of service group (TQG), security and media processing group (SMG), and packet processing group (PPG). Based on this functional grouping, a set of benchmarks called *NpBench*, which includes emerging network workloads especially control plane applications, is presented. Control plane workloads are just emerging and evolving in current network environments, and incorporating them in a benchmark suite helps to design future NPs.

To realize the second objective, characterizations of several network workloads on existing processors are performed. The objective is to understand bottlenecks and identify features of the program that can be exploited while designing network processors. From the characterization results of the control plane application, it can be seen that the control plane applications contain large amounts of instruction level parallelism (ILP). The required computational capability for each network application workloads are also evaluated. It is found that aggressive parallel architectures are required in order to meet the required computational performance of the control plane workloads.

The third and fourth objective consists of identifying architectures for emerging network workloads. Network processors can be used in various node positions with different scales, such as core routers (10 Gbps), edge routers (2.5 Gbps) and access routers (1 Gbps). NPs in different positions will need different architectures. Large scale routers may need a very parallel architecture to meet the required throughput, but it is hard to apply such a complex and expensive architecture to small scale routers. Therefore, a sim-

ple and low priced architecture is required for small scale routers to perform the high throughput workloads

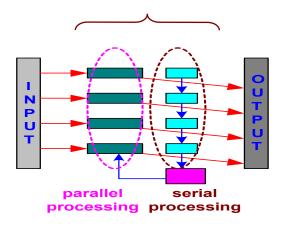

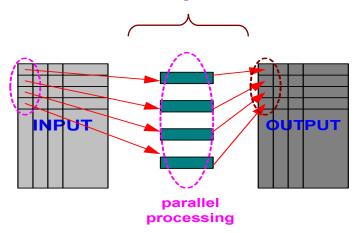

In order to understand the design tradeoffs, a fundamental question, whether parallelism should be identified statically or dynamically, is explored. Dynamically scheduled architectures demand less from compiler, however, if the parallelism is easily amenable for compile-time identification, it is a viable alternative. Current popular media processors - TI's C6x and TriMedia's TM-1300 - rely on the simpler hardware of VLIW processors in order to minimize the cost and power of ILP implementation [4][47][54][55][97][113]. This is because multimedia and DSP applications include many loop operations in the algorithm, and they are well suited for the static scheduling architecture. Network processor workloads have also many iterative algorithm and large parallel characteristics, so statically scheduled architectures are worth considering for NP applications. In this approach, characterizing performance and power dissipation of statically identified ILP implementation are performed, and the characterization results are compared to the dynamic optimization for network processor applications.

The possibilities of hardware acceleration as alternatives for emerging controlplane workloads in network processors are investigated. In this dissertation, the characteristics of control plane applications for network processors are analyzed, and application-specific acceleration techniques are proposed to exploit instruction and data level parallelism.

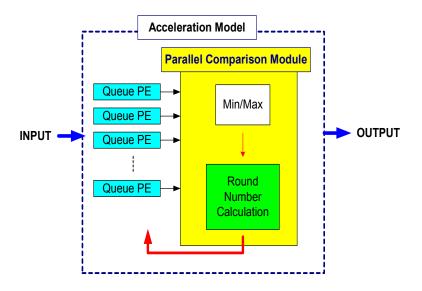

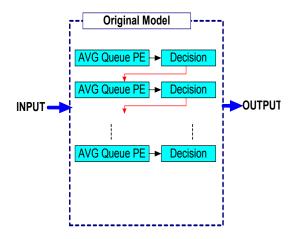

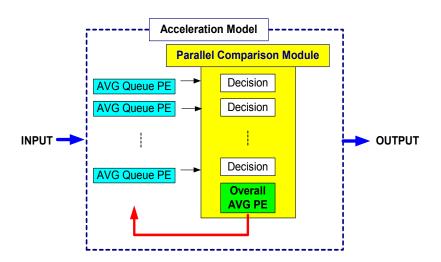

One of the significant application categories is congestion control applications. For this application category, a parallel comparator which decouples serial processing from the queue processing module is applied. The queue processing elements are config-

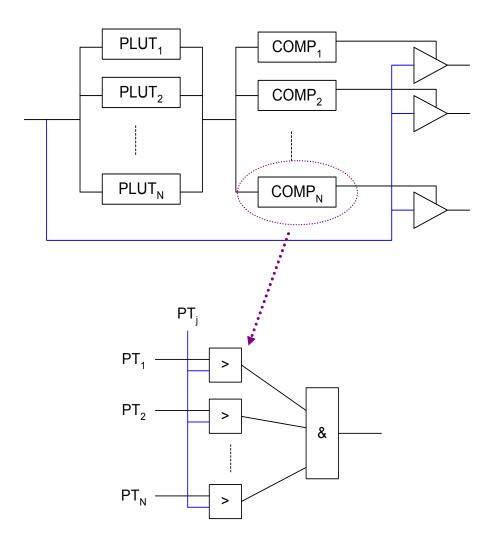

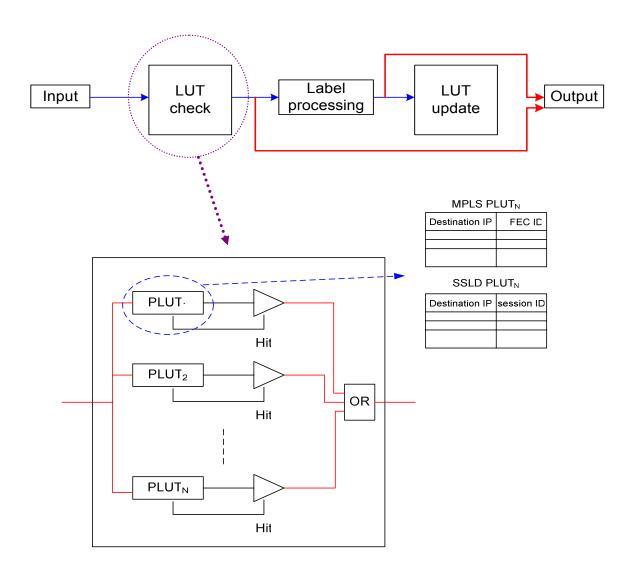

ured in parallel for exploiting packet level parallelism. In media transcoding application category, most of data to be processed in the transcoding proxy are related to multimedia applications, so each processing unit has regular and fine-grained processing element. Therefore, array-style processor is considered as a candidate for accelerating media transcoding. As a third application category, LUT-related applications are also important workloads in control-plane. Based on the analysis, lookup table searching is a major bottleneck in the LUT-related applications. In order to improve this bottleneck, modified partitioned lookup table mechanism is applied to accelerate lookup table searching module. Parallel comparators are used for equality checking to find exactly matched session IDs in SSLD or FEC (forward equivalence class) ID in MPLS.

#### 1.5 THESIS STATEMENT

Modern network workloads involve significant amounts of control plane operations and require more processing than the capability of general purpose processors. Hardware acceleration approaches can deliver the required processing capability at low cost.

#### **1.6 CONTRIBUTIONS**

This dissertation makes several contributions to the defining of a new network processor benchmark suite, the characterization of network processor workloads, the detection of bottlenecks in network workloads, and towards designing architectural alterna-

tives including instruction set extensions, hardware acceleration and statically identified parallel architectures. The summary of the contributions is listed below:

- 1. A benchmark suite, called NpBench targeted towards control plane workloads which are an important part of modern network applications is presented. While previously released network processor benchmarks mainly deal with data plane applications, no benchmark suites are available for control plane workloads. With the increasing demand of QoS [13] and rapidly changing modern network environments, the significance of control plane workloads has become higher. The NpBench suite is implemented using C and is opened to public [64]. Large number of institutions in the world have licensed and several papers and articles cite the NpBench [19][50][77][78][86][88][113][116][118][119]. The benchmark suite is described in [58][64][85].

- 2. The characteristics of network processor workloads such as instruction mix, cache behavior, available parallelism and required processing capability per packet are presented and compared with existing benchmark suites. Several characterization results including architectural characteristics of the application having control plane properties, their implications to designing network processors and the significance of additional parallelism to perform NP applications at wire speed are described. This contribution is described in more detail in [64].

- 3. Parallelism characteristics of network processing applications are compared to multimedia applications. NP applications (e.g. WFQ) have both parallelizable operations and an amount of serial operations, while most of multimedia appli-

- cations have large amount of parallelizable operations. The analysis of these characteristic differences can be a key to improve the throughput of network processors.

- 4. It is investigated whether the success of VLIW in the multimedia field can be applied to the network processor domain as a processing element for a parallel architecture. This premise is analyzed through the comparison between network processor workloads and multimedia workloads in terms of performance (speedup) and power consumption. It is found that NP applications need more aggressive optimization techniques in static scheduled architecture, while media applications can get large parallelism with simple basicblock optimizations. With the characteristics of large packet-level parallelism, experimental analysis supports static scheduling as an applicable paradigm for network processor applications with lower hardware complexity and lower power dissipation. This contribution is described in more detail in [59].

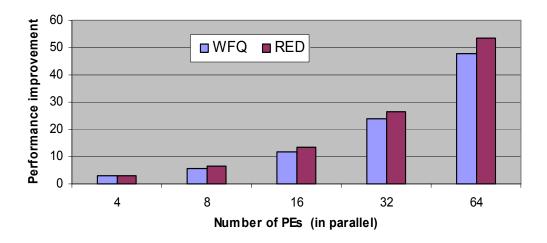

- 5. Congestion control applications contain several parallelizable operations. In order to exploit parallelism of congestion control applications, a hardware acceleration technique is introduced using the decoupling the dataflow into the frontend PLP (Packet level parallelism) module and the back-end hardware acceleration module. This decoupling techniques and defining a hardware acceleration module is done by the thoroughly analysis of the applications. When applying  $16 \sim 64$  acceleration module in parallel,  $10x \sim 50x$  performance improvement is obtained. This contribution is described in more detail in [65].

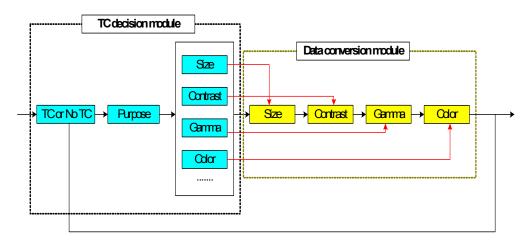

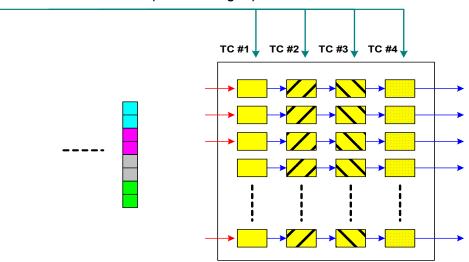

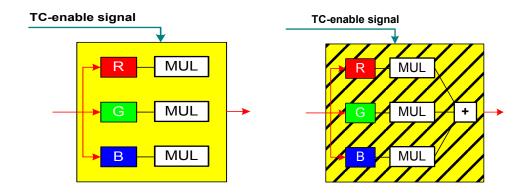

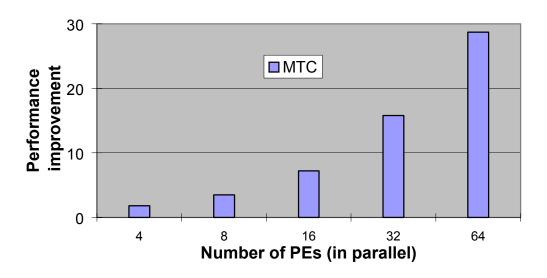

- 6. The procedure of media transcoding consists of transcoding decision unit and pipeline-styled regular processing units for data conversion. The decision module handles which conversion module is enabled and how many modules are enabled. Data conversion modules include several different kinds of functionalities. Based on the experiments, data conversion module takes 89% of the total execution cycles. Most of data to be processed in the transcoding proxy are related to multimedia applications, so each processing unit requires regular and finegrained processing element. Therefore, the systolic-style processor would be a good candidate for accelerating media transcoding. Array-style acceleration technique is proposed for data conversion module of media transcoding applications. If 64 parallel implementation of the acceleration module is applied, it can be obtained approximately 28x speedup in transcoding. This contribution is described in more detail in [60].

- 7. Both SSLD and MPLS have the lookup table searching and updating module in each procedure. Lookup table searching is a major bottleneck in the LUT-related applications (77% ~ 86% of the total execution cycles in MPLS and SSLD). In this dissertation, hardware acceleration techniques are proposed using a partitioned lookup mechanism for searching LUT used in MPLS and SSLD. If 16-way parallel implementation of the acceleration module is applied, 262x improvement for MPLS and 362x for SSLD [60] can be obtained.

- 8. The performance improvement of a single processing element is an important factor in designing parallel architecture. New instruction-set extensions are introduced to support fast execution of congestion control applications, based on

the detailed kernel analysis. Frequently used instructions are combined into one instruction. For congestion control applications, two groups of instruction sets are defined: conditional operations and multiplication-add / multiplication-sub [65]. Proposed architectural extensions show 10~12% improvement in performance for instruction set enhancements.

#### 1.7 ORGANIZATION

The rest of the dissertation is organized as follows:

Chapter 2 describes existing research work pertinent to this dissertation. Previously proposed benchmark suites for network processors are discussed first. Then conventional network processor architectures and industry products are discussed.

Chapter 3 introduces the proposed benchmark suite, called NpBench which includes control plane workloads and data plane workloads. Also, the architectural characteristics of the benchmark are presented and compared to previously released benchmark suite.

Chapter 4 identifies bottlenecks in the execution of network processor applications. This observation is found that the common bottlenecks across both applications are issue width and memory elements.

Chapter 5 discuss whether the success of statically identified parallelism in the multimedia field can be applied to the network processor domain, even though network processor applications have not-so-regular parallel characteristics compared to multime-

dia applications. Effort is also spent in analyzing how these different characteristics in parallelism affect the performance.

Chapter 6 introduces a hardware acceleration technique. Congestion control, media transcoding and LUT related applications are enhanced. For congestion control applications, decoupling the dataflow techniques are introduced. Also, hardware acceleration technique for media transcoding applications and LUT-related applications are presented.

Chapter 7 introduces new ISA extensions to support fast execution of network processing based on the detailed kernel analysis.

Chapter 8 concludes the dissertation by summarizing the contributions and suggesting future opportunities.

#### **Chapter 2: Related Work**

Network processors and related workloads have been researched extensively in the past few years. This chapter discusses prior work to this dissertation. The related work includes several different categories: defining benchmarks, characterizing application's workload, and architectural enhancements to get higher throughput.

#### 2.1 NETWORK PROCESSOR BENCHMARKS

In the network processor fields, there are two benchmarks which were previously proposed: CommBench [122] and NetBench [76]. Wolf, *et al.* [122] presented eight selected workloads called CommBench for traditional routers and active routers. CommBench has two groups of benchmarks namely Header Processing Applications (HPA) and Payload Processing Applications (PPA). Memik, *et al.* [76] proposed nine applications called NetBench for micro-level, IP-level and application-level benchmarks. Nemirovsky [80] also discusses the guidelines for defining benchmarks and challenges of benchmark suites for network processors. He suggests that the benchmark should have two frameworks such as a task-specific benchmark focusing on a single algorithm or protocol and a rich-scenario benchmark containing the complexity of real-life applications. EEMBC [36] and MiBench [44] have some network applications, but they only have routing and encryption applications. NpForum [19][82] has released IA (Implementation

Agreement) on IP Forwarding and IPSec Forwarding application level benchmarks, but as obvious, they focus on forwarding.

Previously proposed benchmarks are mainly focused on data plane workloads. While the benchmarks of data plane applications have been reasonably well understood, there has been very little effort in designing control plane workloads that perform congestion control, flow management, higher-level protocols and other control tasks. Control plane workloads are just emerging and evolving in current network environments. The NpBench suite presented in this dissertation is mostly focusing on control plane applications. Also, characteristics of control plane workloads from architectural aspects are analyzed.

#### 2.2 ARCHITECTURAL CHARACTERISTICS OF NETWORK PROCESSOR APPLICATIONS

Past studies using CommBench [122] and NetBench [72] contrast network workloads with other benchmarks, such as SPEC [102] and mediabench [66], with respect to instruction set characteristics and memory behaviors. Wolf, *et al.* [122] indicate that network processors must deal with both streaming and header processing applications. Memik, *et al.* [76] insist that network processor applications have a data-intensive nature. In terms of load/store instruction ratio, the NetBench applications make high number of memory accesses, while MediaBench applications has more frequent branch instructions resulting in a lower instruction level parallelism.

#### 2.3 NETWORK PROCESSOR ARCHITECTURES

In order to deal with variety of application areas for network processors, there could be a wide range of NP architectures and implementations. Each company is applying their own architectural concepts in the implementation of network processors. For the enterprise service, several companies developed RISC-based NP with ASIC blocks for networking functions such as IXP 1200/2000 series by Intel [52], CXE-16 by Switchcore, CS2000 by Chameleon etc. For the high-end service, Motorola (C-port) [27], Lucent (FPP/RSP) [71], EZChip (NP-1) [37] and Vitesse/ Sitera(IQ2000) have used network-specific ASICs with the features of network classifying, QoS, etc. Some companies like Chrysalis-ITS, Alliance, NetLogic have developed co-processors with the functions such as routing table, classification or cryptography [96].

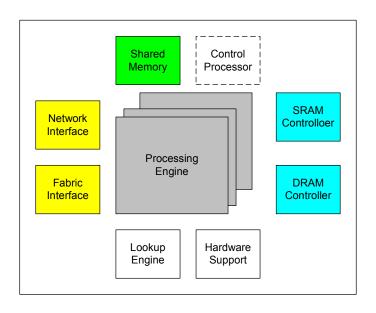

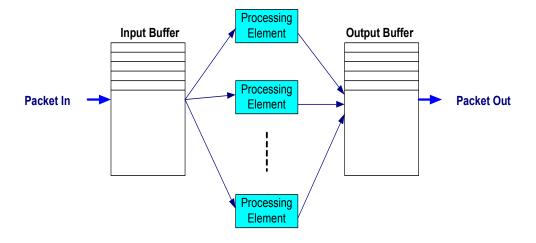

Most of NP architectures employ multiple processing engines (PEs), even though they each have different names such as micro engine, channel processor or task optimized processor. Some are based on RISC cores having their PEs arranged in parallel or in a pipelined fashion. The alternative to the RISC is the VLIW based architecture, in which most of the PEs are organized in a pipelined method. Many RISC based NPs employ multithreading on their PEs to maximize the performance. To ensure fast context switching between tasks, the NP should have hardware support for multithreading. Figure 2.1 shows an overall architecture of typical network processor. In general, control and management functions have more complex processing requirements than data functions. GPPs have been used as control processors in commercial network products. Many NPs provide the function of control processor with an integrated core or externally via a host

interface [49]. In this dissertation, it is shown that GPPs do not have enough processing capability to come up with increased demand for complex processing and higher data rates.

Figure 2.1 Overall architecture of NP

Related recent research and commercial products for network processors show the use of multithreading and vector-type array processing. Melvin, *et al.* [74] utilize multiple multithreaded processing engines to get a high degree of thread-level parallelism (TLP) in an NP design that supports 256 simultaneous threads in eight processing engines. In this scheme, each thread has its own independent register file, while sharing functional resources and memory ports with other threads. ClearSpeed [24] introduces an MTAP (Multi-Threaded Array Processing) processor, which provides a scalable processing solution, based on an array of 10s to 1,000s of small processing elements. Each PE has its own local memory and I/O capability. Although these implementations can meet

the required performance, they have large amounts of hardware complexity, cost and power issues.

Shah, et al. [96] indicate that today's network implementations are based on Field Programmable gate Arrays (FPGAs) for lower level processing and General Purpose Processors (GPPs) for higher layer processing. They also investigate the broad categories of alternatives for system implementations such as ASIC (Application Specific Integrated Circuit), ASIP (Application Specific Instruction Processor), Co-processor, FPGA and GPP. They also present the diversity among different network processors. For example, IBM and Motorola have co-processors for most packet-processing kernels, while Cognigine relies on the reconfigurable functional units. EZchip has entire processors devoted to pattern matching, lookup, data manipulation, and queue management. Agere's PayloadPlus system uses a special processor for pattern matching and data manipulation, a co-processor for checksum/CRC computation, and has memory features for queue management. Vitesse and Xelerated Packet Devices simply use a mix of co-processors and functional units. Intel and Lexra also include special memory and bus features and have a dedicated processor for the control-plane.

# Chapter 3: Development and Characterization of a Network Processor Benchmark Suite

It is important to have a benchmark suite with emerging network workloads in order to design future network processors. A good benchmark suite must contain emerging and futuristic workloads in order to prevent it from being outdated very quickly. Designing future processors with benchmarks of today, which are programs of yesterday, often results in processors and systems which cannot handle workloads that are prevalent when the processor design is finished.

This chapter presents NpBench, a benchmark suite that was developed to assist designers of future network processor designers. Predictions on future workloads are very difficult to make, however one can examine trends to make educated guesses on what might be probable network workloads a few years from now. The NpBench benchmark suite was created by studying applications from modern network domain workload. A concern that many network processor designers have is that the control plane processing content of network workloads is going up, while the current network benchmarks do not represent that. Hence a study of emerging network applications was conducted, with an emphasis on control plane processing.

#### 3.1 INVESTIGATION OF MODERN NETWORK WORKLOADS

Network applications perform routing, scheduling, traffic management/congestion control, quality of service enforcement, security management, packet processing, etc. A survey of the functionality of modern network applications reveal applications in three major functional groups: traffic-management and quality of service group (TQG), security and media processing group (SMG), and packet processing group (PPG). A categorization of major network applications into these categories is presented in Table 3.1. The table also illustrates whether the application includes control plane content. Since control plane processing is increasing in modern networks, it will be important to include sufficient amount of control plane applications into the benchmark suite.

The investigation of the network workloads unveiled various kinds of applications that in use today or those which are expected to be popular in future. However, not much information is available regarding a mix of these applications in real-world routers. Predicting the mix of applications that will be popular in a network workload a few years from now, is difficult and is outside the scope of this dissertation. The objective of this research will only be to develop source code for a variety of applications that are expected to be popular, and to make it available to other researchers and designers.

It is often impractical to include every application in the world into a benchmark suite. It is often sufficient to choose representative applications for the major classes of applications. In order to decide what applications must be selected into the benchmark suite, information on the workloads used by network routers in the real world was collected. Cisco Systems Incorporation is the biggest router provider and hence an investigation of their applications can provide valuable information on what is important in current

and future network environments. Information from CISCO [23][21], Lightsurf [73] and IBM [8] was used in making some deductions on emerging network workloads.

Table 3.1 Functional grouping of network processor workloads

| Group                     | Applications               | Data<br>Plane | Control<br>Plane |

|---------------------------|----------------------------|---------------|------------------|

|                           | Routing                    | X             | X                |

|                           | Scheduling                 | X             | X                |

|                           | Content-based switching    | X             | X                |

| TQG                       | Weighted fair queuing      | X             | X                |

| (Traffic-management and   | Traffic shaping            | X             | X                |

| Quality-of-Service        | Load balancing             | X             | X                |

| Group)                    | VLAN                       |               | X                |

| Group)                    | MPLS                       | X             | X                |

|                           | RSVP                       | X             | X                |

|                           | DiffServ                   | X             | X                |

|                           | IntServ                    | X             | X                |

|                           | Block cipher algorithm     | X             |                  |

|                           | Message digest algorithm   | X             |                  |

|                           | Firewall application       | X             | X                |

| SMG                       | IPSec                      | X             | X                |

| (Security and             | Virtual private network    | X             | X                |

| Media Processing Group)   | Public encryption          | X             |                  |

| Wiedla i focessing Group) | Usage-based accounting     | X             | X                |

|                           | H.323                      | X             |                  |

|                           | Media transcoding          | X             | X                |

|                           | Duplicate data suppression | X             |                  |

|                           | IP-packet fragmentation    | X             |                  |

| PPG                       | Packet encapsulation       | X             |                  |

| (Packet Processing        | Packet marking/editing     | X             |                  |

| Group)                    | Packet classification      | X             |                  |

|                           | Checksum calculation       | X             |                  |

Weighted fair Queuing (WFQ) is one of Cisco's premier queuing techniques [23]. For situations in which it is desirable to provide consistent response time to heavy and

light network users without adding excessive bandwidth, the solution is WFQ. It is a flow-based queuing algorithm, and it can work in conjunction with RSVP (Resource Reservation Protocol) to build Integrated Service architecture implementations which are designed to guarantee network bandwidth from end to end for IP networks. Hence WFQ was included in the NpBench suite.

Random Early Detection (RED) is useful on any output interface where expected to have congestion. RED is usually used in the core routers of a network, rather than the network's edge. Edge routers assign IP precedences to packets as they enter the network. Cisco's RED implementations include Distributed Weighted Random Early Detection [23], which combines the capabilities of the RED algorithm with IP Precedence. This combination provides for preferential traffic handling for higher priority packets. WRED provides separate thresholds and weights for different IP precedences, which can provide different qualities of service for different traffic. It is not known whether RED will be used heavily in the future, but RED is included in the suite because if traffic management becomes critical, RED is likely to be employed.

Cisco's IOS Multiprotocol Label Switching (MPLS) enables Enterprises and Service Providers to build next-generation intelligent networks that deliver a wide variety of advanced, value-added services over a single infrastructure [21]. This economical solution can be integrated seamlessly over any existing infrastructure, such as IP, Frame Relay, ATM, or Ethernet. Subscribers with differing access links can be aggregated on an MPLS edge without changing their current environments, as MPLS is independent of access technologies. Integration of MPLS application components, including VPN, Traffic Engineering, QoS and IPv6 enable the development of highly efficient, scalable, and se-

cure networks that guarantee Service Level Agreements. MPLS appears to be a likely component of future network workloads and hence it is included in the suite.

Another popular application appeared to be SSL (Secure Socket Layer), the defacto standard in securing distributed applications [8]. Originally defined by Netscape Communications, SSL is accepted for network applications for authenticated and encrypted communication between clients and servers. The SSL protocol runs above TCP/IP and below higher-level protocols such as HTTP. It uses TCP/IP on behalf of the higher-level protocols, which allows an SSL-enabled server to authenticate itself to an SSL-enabled client, allows the client to authenticate itself to the server, and allows both machines to establish an encrypted connection. These capabilities address fundamental concerns about communication over the Internet and other TCP/IP networks. SSLD is a technology to reduce the load of authentication between server and client.

A significant part of network workloads appear to be handling multimedia data. Often, data exists in one format at a server, and has to be displayed in a simpler format on a mobile device. Media transcoding (MTC) delivers optimized pictures and other multimedia content across wide range of heterogeneous devices. LightSurf [73] provides a media transcoing product which senses what kind of viewing device the recipient is using and intelligently transcodes the images and other multimedia files for optimal delivery. Throughout the world, there are hundreds of different graphics-capable mobile phones that all have varying display characteristics. Cisco [23] also provides Media Resource Manager (MRM) as resource reservation of transcoders within a Cisco CallManager cluster. Cisco CallManager supports simultaneous registration of both Media Transfer Part

(MTP) and transcoder and concurrent MTP and transcoder functionality within a single call.

Security is another major issue in networks and security applications are expected to be a major component of future network workloads. IPSec is a framework of open standards developed by the Internet Engineering Task Force (IETF) that provides security for transmission of sensitive information over unprotected networks such as the Internet [23]. In the case of secure VPN client IPSec, as the tunnel comes up, the PC receives its IP address from the central router's IP address pool, then the pool traffic can reach the local or be routed and encrypted to the network behind the outlying router. IPSec provides a more robust security solution and is standards-based. IPSec also provides data authentication and anti-replay services in addition to data confidentiality services.

Packet processing applications are essential and an important part of modern network workloads. Every packet-based network has an MTU (Maximum Transmission Unit) size. The MTU is the size of the largest packet network can transmit. Packets larger than the allowable MTU must be divided into multiple smaller packets, or fragments, to enable them to traverse the network. Packet fragmentation appears to be an essential application for packet processing.

Error detection and correction is an important part of network processing. Cycle redundancy check (CRC) is a technique used to check errors. The CRC uses a calculated numeric value to detect errors in transmitted data. The sender of a data frame calculates the Frame Check Sequence (FCS). The sender appends the FCS value to outgoing messages. The receiver recalculates the FCS, and compares it with the FCS from the sender. If a difference exists, the receiver assumes that a transmission error occurred, and

sends a request to the sender to re-send the frame. The retention of the true value of a frame is important to ensure that the destination correctly interprets the data over the network. CRC is another essential application for packet processing.

Based on this analysis, ten representative applications are chosen from the functional groups for the first version of NpBench suite as shown in Table 3.2. The suite includes several control plane functions as they are missing from the available NP workloads.

Table 3.2 Benchmarks in the NpBench suite

| Group | Application                                                                                                                                                | Description                                                                                                                                          |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | WFQ                                                                                                                                                        | Weighted Fair Queuing is a queue scheduling algorithm                                                                                                |  |  |  |  |  |

|       | RED                                                                                                                                                        | Random Early Detection is an active queue management algorithm which drops arriving packets probabilistically                                        |  |  |  |  |  |

| TQG   | SSLD                                                                                                                                                       | Secure Sockets Layer Dispatcher is an example of content-<br>based switching mechanism                                                               |  |  |  |  |  |

|       | MPLS                                                                                                                                                       | Multi Protocol Layer Switching is a forwarding technology using short labels                                                                         |  |  |  |  |  |

|       | MTC Media Transcoding is the process that a media object in one representation is converted into another representation for value spectrum of client types |                                                                                                                                                      |  |  |  |  |  |

|       | AES                                                                                                                                                        | Advanced Encryption Standard (RijnDael) is a block cipher that encrypts and decrypts 128, 192 and 256 bits blocks                                    |  |  |  |  |  |

| SMG   | MD5                                                                                                                                                        | Message Digestion algorithm takes as input a message of arbitrary length and produces as output a 128-bit fingerprint or message digest of the input |  |  |  |  |  |

|       | DH                                                                                                                                                         | Diffie-Hellman key exchange allows two parties who have not met to exchange keys securely on an unsecure communication path                          |  |  |  |  |  |

|       | FRAG                                                                                                                                                       | FRAG is a packet fragmentation application                                                                                                           |  |  |  |  |  |

| PPG   | CRC                                                                                                                                                        | Cyclic Redundancy Check is used in Ethernet and ATM Adaptation Layer 5 (AAL-5) checksum calculation                                                  |  |  |  |  |  |

Some of these selected applications are implemented to form the current release of the NpBench suite and the rest of them are referred from open source code sites or other benchmarks [44][66][122]. The C code for the benchmarks is available on request [85].

### 3.2 DESCRIPTION OF THE APPLICATIONS IN THE NPBENCH SUITE

## 3.2.1 Traffic-management and QoS Group (TQG) Benchmarks

TQG benchmarks have a set of applications related to routing, scheduling, queuing, switching, signaling and quality of services. These applications contain both control plane processing and data plane processing. The first two benchmarks, WFQ and RED are congestion control algorithms. In general, congestion occurs at a router when incoming packets arrive at a rate faster than the rate the router can switch them to an outgoing link. The two representative algorithms for congestion control are the scheduling algorithm and the queue management algorithm [15][39]. The scheduling algorithm determines which packet to be sent next and is used primarily to manage the allocation of bandwidth among flows (e.g., weighted fair queuing). According to the IETF (Internet Engineering Task Force) recommendation [15], the default mechanism for managing queue lengths to meet these goals in FIFO queues is the RED algorithm. SSLD is a content-based switching algorithm and MPLS is a technology used for quick forwarding of packets across backbones.

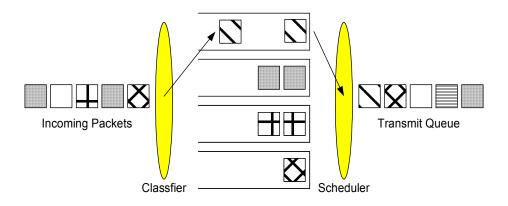

WFQ (Weighted Fair Queuing): WFQ [11][14][30][105] is a queue-scheduling algorithm to serve packets in order of their finish-times considering the weight on connections. As shown in Figure 3.1, various lengths of packets from incoming traffic are classified into different queues, which can be used for differential service. And they are scheduled by a specific mechanism that determines packets to be sent from the queues. WFQ uses each packet's estimated finish-time to decide packets to be sent.

Figure 3.1 WFQ (Weighted Fair Queuing)

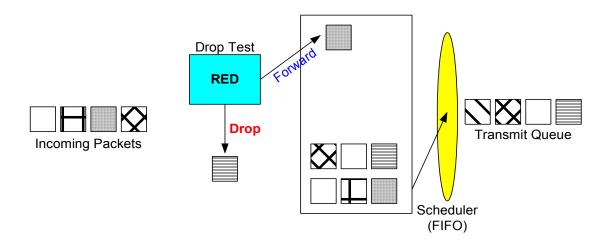

**RED** (Random Early Detection): RED [15][39] is an active queue management algorithm for routers. In contrast to the traditional queue management algorithm, which drops packets only when the buffer is full, the RED algorithm drops arriving packets

probabilistically before coming into the queue as shown in Figure 3.2. The decision of whether or not to drop an incoming packet is based on the estimation of the average queue size.

Figure 3.2 RED (Random Early Detection)

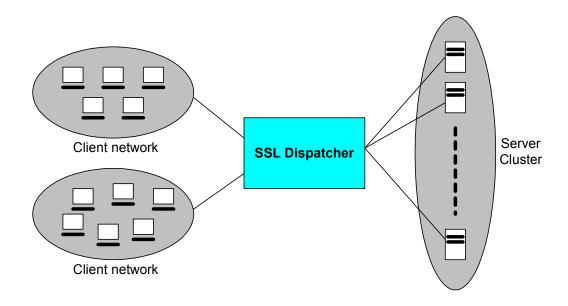

**SSLD (SSL Dispatcher)**: SSLD [7][99][102] is one example of content-based switching mechanism in the server and client cluster environments. SSL typically runs over TCP (Transmission Control Protocol), which is used for secure processing of e-commerce applications. Once TCP connection is established, SSLD maintains the session ID information during authentication process, sharing the SSL information among the nodes in cluster. When reconnecting to the same server, a client can reuse the session

state established during a previous SSL handshake which makes the workloads computationally heavy. Figure 3.3 shows the concept of SSL dispatcher.

Figure 3.3 SSLD (SSL Dispatcher)

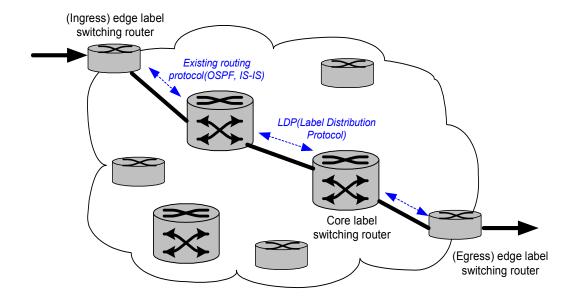

MPLS (Multi Protocol Label Switching): MPLS [9][56][79][93][126] is a forwarding technology, which does away with the lookup of bulky IP headers and uses short labels for forwarding at the edge of the MPLS domain as shown in Figure 3.4. In this version of NpBench, two control plane aspects of MPLS such as Label Distribution and Label Generation, are used. Two functions are extracted from MPLS, namely an upstream routing function (for an ingress edge router or a core router) and a downstream routing function (for a core router or an egress router).

Figure 3.4 MPLS (Multi Protocol Label Switching)

# 3.2.2 Security and Media processing Group (SMG) Benchmarks

As the e-commerce industry has grown, the security and the accounting applications such as firewall application, admission control, encryption applications and usage based accounting, have become an emerging workload. With higher bandwidth, the demand for high quality of multimedia service is increased. Data stream manipulation, media transcoding, H.323 and several encoding applications [61][62] can be important issues of NP, associated with QoS. For security benchmarks, three components of IPSec

[19][33][95] – Authentication Header (AH), Encapsulating Security Payload (ESP) and key management – are included in SMG.

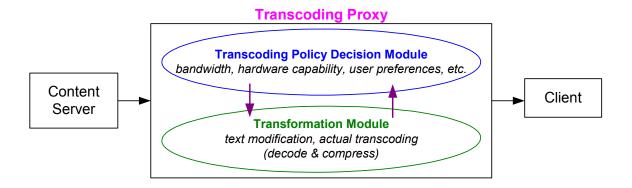

MTC (Media TransCoding): Media Transcoding [46][99] is a process in which a data object in one representation is converted into another representation. In order to accommodate the wide spectrum of client capabilities, the media data is modified along the dimensions, fidelity, and resolution. As shown in Figure 3.5, media transcoding consists of transcoding policy decision module and transcoding module. The transcoding policy decision module decides which factors should be converted to another representation based on client device information, contents information and network environments. The transcoding module deals with actual conversion processing.

AES (Advanced Encryption Standard): Advanced Encryption Standard (RijnDael) [1][44] is a block cipher that encrypts and decrypts 128, 192 and 256 bit blocks, which is a U.S. government standard for encryption and digital signature. It is used for implementation of AH in IPSec. AES, designed by Joan Daemen & Vincent Rijmen, is a block cipher using symmetric key. It is fast and scalable, and it is also resistant to all known cryptanalysis attacks. Decryption is 30% slower than encryption, since inverse matrix calculation is more complicated. In the algorithm, the block is considered to be structured as 4, 6 or 8 columns of 4 bytes, depending on block size. The basic operations applied to the block are KeyAddition, Substitution, ShiftRow and MixColumn.

Figure 3.5 MTC (Media Transcoding)

MD5 (Message Digestion): MD5 algorithm [44][122] takes a message of arbitrary length as an input and produces a 128-bit "fingerprint" or "message digest" as an output. MD5 is a method to verify data integrity and is more reliable than checksum method. It is used to perform ESP in IPSec. An algorithm created in 1991 by Professor Ronald Rivest that is used to create digital signatures. It is intended for use with 32 bit machines and is safer than the MD4 algorithm, which has been broken. MD5 is a one-way hash function, meaning that it takes a message and converts it into a fixed string of digits, also called a message digest. When using a one-way hash function, one can compare a calculated message digest against the message digest that is decrypted with a public key to verify that the message hasn't been tampered with. This comparison is called a "hashcheck."

**DH** (**Diffie-Hellman**): Diffie-Hellman [44][76][122] key exchange allows two parties who have not met, to exchange keys securely on an unsecured communication path. Typically DH is used to exchange a randomly generated conventional encryption key, the rest of the exchange is then encrypted with the conventional cipher. It is applied to the function of key management in IPSec. Diffie-Hellman key exchange allows two parties who have not met to exchange keys securely on an unsecure communication path. It has been used with DES, 3DES, IDEA, RC4 though basically the approach of using DH key exchange can be used for any conventional stream or block cipher. PGP itself operates in a similar fashion, except that PGP uses RSA for key exchange, and IDEA as the conventional cipher.

# 3.2.3 Packet Processing Group (PPG) Benchmarks

Packet processing group includes IP packet fragmentation, packet marking, editing and classification. Most applications are data plane processing.

**FRAG (Packet Fragmentation)**: FRAG [122] is a packet fragmentation application. IP packets are split into multiple fragments for which some header fields have to be adjusted and a header checksum computed.

**CRC** (Cyclic Redundancy Check): 32-bit Cyclic Redundancy Check [44] is used in Ethernet and ATM Adaptation Layer 5 (AAL-5) checksum calculation.

In summary, the NpBench suite consists of both essential workloads widely used in real world and emerging workloads starting to be used in real applications or services. Some of control plane workloads including WFQ, RED and MPLS are used in real world, while SSLD and MTC are emerging workloads which will be significant workloads in routers. These emerging applications will be widely used at routers as Internet business and wireless technologies are evolving. In the data plane workloads, three IPSec applications are very important in all security-related areas including banking, personal identification and e-commerce applications. FRAG and CRC are basic and essential operations for packet processing.

#### 3.3 IMPLEMENTATION

The NpBench control-plane functions such as WFQ, RED, SSLD, MPLS and MTC at the application level are developed using C language, and most of the data-plane functions such as FRAG, CRC and IPSec applications were extracted from pen source code or other benchmarks [44][66][76][122].

Randomly generated packets are used as input of the benchmark. For TQG benchmarks, WFQ uses packet size and queue information as an input. RED uses incoming packet size and average queue size to decide whether the packet is to be dropped or put in the FIFO queue. The clientHello message and serverHello message of the SSL protocol [102] are used with randomly generated session ID information for the experiment of SSLD. The values of FEC identification number are used for two MPLS functions. The RED implementation allows an option of congestion environment, which is con-

trolled by transmission rate of the queue. The SSLD inputs can be different session IDs with different reusability factors. In SMG benchmarks, MTC can be separated into two components which are policy modules to get adaptive transcoding policies and transformation modules to perform real transcoding. The policy decision module can be executed independently with an execution option. AES can use any files as an input data and MD5 can make a fingerprint of any files or strings for the input. DH generates and exchanges for any number of Diffie-Hellman key pairs. For PPG benchmarks, FRAG and CRC employ randomly generated IP header as an input data. Under the above simulated network environments, the characteristic of NpBench is investigated and presented at next section.

## 3.4 ARCHITECTURAL CHARACTERISTICS OF NPBENCH WORKLOADS