Copyright by Shiwen Hu 2005

# The Dissertation Committee for Shiwen Hu Certifies that this is the approved version of the following dissertation:

# Efficient Adaptation of Multiple Microprocessor Resources for Energy Reduction Using Dynamic Optimization

**Committee:**

Lizy K. John, Supervisor

Tony Ambler

Mauricio Breternitz Jr.

Stephen W. Keckler

Kathryn S. McKinley

David Z. Pan

### Efficient Adaptation of Multiple Microprocessor Resources for Energy

### **Reduction Using Dynamic Optimization**

by

Shiwen Hu, B.E.; M.S.

### Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### **Doctor of Philosophy**

The University of Texas at Austin December 2005

## Dedicated

To my wife Yi Lu.

### Acknowledgements

First I would like to thank my advisor, Dr. Lizy K. John, for her support, advice, guidance and good wishes. Her availability at all times including on weekends, and her dedication to work has had a profound influence not only on my academic pursuit, but also on my life. I am also grateful for the freedom and the flexibility she gave me throughout my Ph.D. study.

My gratitude goes to the committee members (in alphabetical order), Dr. Tony Ambler, Dr. Mauricio Breternitz Jr., Dr. Steve Keckler, Dr. Kathryn S. McKinley, and Dr. David Z. Pan, for their invaluable comments, productive suggestions, and the time to read the draft of my thesis.

I would like to thank the students (past and current) at the Laboratory for Computer Architecture -- Tao, Madhavi, Juan, Ravi, Yue, Byeong, Aashish, Ajay, Sean, Hari, and Dimitry. They provided valuable feedback on the drafts of my paper submissions and on my practical talks. I enjoyed working with Ravi and Madhavi in writing the research papers.

Thanks to Debi, Amy, Melanie and other administrative assistants who worked in the Department in the past years.

Last but not least, I am grateful to my wife, Yi, for her consistent love, support, and encouragement throughout my graduate years. This is not something I could accomplish alone.

# Efficient Adaptation of Multiple Microprocessor Resources for Energy Reduction Using Dynamic Optimization

Publication No.\_\_\_\_\_

Shiwen Hu, Ph.D. The University of Texas at Austin, 2005

Supervisor: Lizy K. John

The continuing advances in VLSI technology have fueled dramatic performance gains for general-purpose microprocessor, but microprocessor energy consumption has been increasing substantially in the past decade. The steady increase of microprocessor energy consumption significantly affects circuit reliability, cooling and package costs, and battery life of embedded systems.

Adaptive microarchitectures are one of the commonly used techniques to dynamically identify configurations that are desirable from performance and power perspectives. By matching hardware resources to a program's runtime requirements, adaptive microarchitectures can effectively reduce energy with minimal performance loss. However, the task of searching for the most energy efficient configurations is complicated by configuration space explosion, which may considerably impair an adaptive microarchitecture's performance and energy efficiency.

This dissertation presents a hardware adaptation framework for efficient management of multiple configurable units, utilizing a dynamic optimization system's inherent capabilities of detecting and optimizing dominant code regions (*hot spots*). The

framework uses hot spot boundaries for phase detection and hardware adaptation. Since hot spots are of variable sizes and are often nested, the framework can decouple the reconfiguration of CUs with diverse adaptation costs by adjusting the granularity of adaptation based on each CU's reconfiguration cost.

This dissertation also studies the interference imposed by one CU's configuration changes on others' adaptation. CUs with minimal mutual interference can be adapted in parallel. In addition, for some CUs, one's size reduction usually prompts the other to choose a smaller size for energy reduction. Hence, the search of those CUs' best configurations biases toward certain paths, and thus prunes the tuning space. Employing the tuning-reduction strategies, the proposed framework significantly improves the energy efficiency of an adaptive microarchitecture.

The energy and hardware adaptation impact of two important dynamic optimization services, JIT optimization and garbage collection, are also investigated in this work. By stressing the data caches, both dynamic optimization services decrease the average power dissipated by a dynamic optimization system. Furthermore, owing to their distinct runtime characteristics and their capabilities to alter program runtime behavior, the two dynamic optimization services change the adaptation preferences of configurable hardware units, and influence the energy efficiency of an adaptive microarchitecture.

### **Table of Contents**

| List of Tables                                                    | xi      |

|-------------------------------------------------------------------|---------|

| List of Figures                                                   | xiii    |

| Chapter 1. Introduction                                           | 1       |

| 1.1 Microprocessor energy reduction                               | 1       |

| 1.2 Adaptive microarchitectures                                   | 2       |

| 1.3 Efficient management of multiple configurable units           | 3       |

| 1.4 Thesis statement                                              | 5       |

| 1.5 Contributions                                                 | 5       |

| 1.6 Organization                                                  | 10      |

| Chapter 2. Background and Related Work                            | 11      |

| 2.1 Configurable hardware units                                   | 11      |

| 2.1.1 Issue queue                                                 | 12      |

| 2.1.2 Reorder buffer                                              | 13      |

| 2.1.3 Cache hierarchy                                             | 14      |

| 2.1.4 Other hardware units                                        | 16      |

| 2.2 Program phase detection                                       | 17      |

| 2.3 Resource adaptation strategies                                | 21      |

| 2.4 Dynamic optimization systems                                  | 22      |

| 2.4.1 Jikes Research Virtual Machine (RVM)                        | 23      |

| 2.4.2 Other dynamic optimization systems                          | 24      |

| 2.4.3 Hot spot detection and optimization                         | 26      |

| 2.5 Power-aware compiler optimizations                            | 27      |

| Chapter 3. Hardware Adaptation Framework based on Dynamic Optimiz | ation29 |

| 3.1 Hot spot detection                                            | 30      |

| 3.2 CU decoupling and hot spot tuning                             | 31      |

| 3.2.1 CU decoupling                                               | 31      |

| 3.2.2 Hot spot tuning                                             | 32      |

| 3.3 Hardware reconfiguration                                   |    |

|----------------------------------------------------------------|----|

| 3.4 Hardware support                                           |    |

| 3.5 Differences with prior approaches                          |    |

| 3.6 Applicability                                              |    |

| Chapter 4. Experimental Methodology                            |    |

| 4.1 Simulation environment                                     |    |

| 4.1.1 Dynamic Simplescalar                                     |    |

| 4.1.2 Basic block vector phase detection                       |    |

| 4.1.3 Configurable hardware units                              | 40 |

| 4.2 Dynamic optimization system                                | 42 |

| 4.3 Benchmarks                                                 | 43 |

| Chapter 5. Evaluation of the Hardware Adaptation Framework     | 44 |

| 5.1 Runtime characteristics of hot spots and BBV phases        | 45 |

| 5.1.1 Runtime characteristics of hot spots                     | 45 |

| 5.1.2 Runtime characteristics of BBV phases                    | 47 |

| 5.2 Adaptation of five configurable units                      |    |

| 5.2.1 Runtime characteristics                                  | 51 |

| 5.2.2 Energy reduction                                         |    |

| 5.2.3 Performance impact                                       | 55 |

| 5.3 Adaptation efficiency                                      | 57 |

| 5.3.1 Adaptation of issue queue and reorder buffer             |    |

| 5.3.2 Adaptation of L1D, L1I, and L2 caches                    | 60 |

| 5.3.3 Adaptation efficiency                                    | 61 |

| 5.3 Summary of advantages                                      | 63 |

| 5.4 Discussion                                                 | 64 |

| Chapter 6. Analysis of Factors that Interfere with Adaptation  | 67 |

| 6.1 Impact of runtime characteristics on CUs' tuning decisions | 67 |

| 6.1.1 Impact measurement                                       | 67 |

| 6.1.2 Impact intensity analysis                                |    |

| 6.1.3 Implications to tuning process reduction                 | 73 |

| 6.2 Interference between configurable units                                                                            | 75   |

|------------------------------------------------------------------------------------------------------------------------|------|

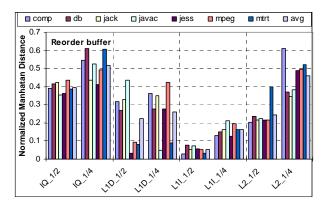

| 6.2.1 Interference distance measurement                                                                                | 75   |

| 6.2.2 Interference distances between CUs                                                                               | 76   |

| 6.2.3 Implications to tuning process reduction                                                                         | 81   |

| 6.3 Reduction of multi-CU tuning process                                                                               | 82   |

| 6.3.1 Tuning reduction strategies                                                                                      | 83   |

| 6.3.2 Evaluation of the tuning reduction strategies                                                                    | 85   |

| 6.4 Discussion                                                                                                         | 89   |

| 6.4.1 Generalized tuning reduction algorithm for independent CU                                                        | Js90 |

| 6.4.2 Generalized tuning reduction algorithm for CUs with positi interference                                          |      |

| Chapter 7. The Role of JIT Optimization and Garbage Collection on Microp<br>Energy Consumption and Hardware Adaptation |      |

| 7.1 Energy impact of JIT optimization and garbage collection                                                           | 94   |

| 7.1.1 Impact of JIT optimization                                                                                       | 95   |

| 7.1.2 Impact of garbage collection                                                                                     | 101  |

| 7.1.3 Key insights                                                                                                     | 108  |

| 7.2 Interference of JIT optimization and garbage collection on hardwa adaptation                                       |      |

| 7.2.1 Interference of JIT optimization                                                                                 | 109  |

| 7.2.2 Interference of garbage collection                                                                               | 112  |

| 7.3 Discussion                                                                                                         | 117  |

| Chapter 8. Conclusions and Future Research                                                                             |      |

| 8.1 Conclusions                                                                                                        | 119  |

| 8.2 Directions for Future Research                                                                                     | 123  |

| Bibliography                                                                                                           | 126  |

| Vita                                                                                                                   | 134  |

### List of Tables

| Table 1. Baseline configuration of the simulated system.    38                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2. Configurable hardware units and their adaptation parameters.         40                                                                    |

| Table 3. Characteristics of SPECjvm 98 benchmarks executed by Jikes RVM43                                                                           |

| Table 4. Runtime hot spot characteristics of SPECjvm 98 benchmarks                                                                                  |

| Table 5. Runtime characteristics of hot spots in three different size ranges                                                                        |

| Table 6. Runtime characteristics of stable BBV phases with 10K and 1M sampling                                                                      |

| intervals49                                                                                                                                         |

| Table 7. Runtime characteristics while adapting the five configurable units52                                                                       |

| Table 8. Adaptation efficiency retained by the 5-CU system versus the 2/3-CU                                                                        |

| system                                                                                                                                              |

| Table 9. Coefficients of variations for the characteristic/CU pairs that possess the                                                                |

|                                                                                                                                                     |

| monotonic property74                                                                                                                                |

| monotonic property74<br>Table 10. Performance, energy and power of JIT optimized system as fractions of the                                         |

|                                                                                                                                                     |

| Table 10. Performance, energy and power of JIT optimized system as fractions of the                                                                 |

| Table 10. Performance, energy and power of JIT optimized system as fractions of the corresponding results of un-optimized system.                   |

| Table 10. Performance, energy and power of JIT optimized system as fractions of the corresponding results of un-optimized system                    |

| <ul> <li>Table 10. Performance, energy and power of JIT optimized system as fractions of the corresponding results of un-optimized system</li></ul> |

| <ul> <li>Table 10. Performance, energy and power of JIT optimized system as fractions of the corresponding results of un-optimized system</li></ul> |

| <ul> <li>Table 10. Performance, energy and power of JIT optimized system as fractions of the corresponding results of un-optimized system</li></ul> |

| <ul> <li>Table 10. Performance, energy and power of JIT optimized system as fractions of the corresponding results of un-optimized system</li></ul> |

| Table 15. Hardware units' energy consumption in JIT optimized system as frac | tions |

|------------------------------------------------------------------------------|-------|

| of those of un-optimized system                                              | 109   |

| Table 16. Fixed size hardware units' energy consumption with small heaps as  |       |

| fractions of those with 200M heap                                            | 113   |

# List of Figures

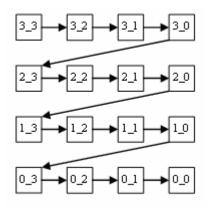

| Figure 1. Adaptation of two four-configuration hardware units. (Each pair of numbers |

|--------------------------------------------------------------------------------------|

| is one combinational configuration, with the numbers indicating the two              |

| CUs' individual configurations.)4                                                    |

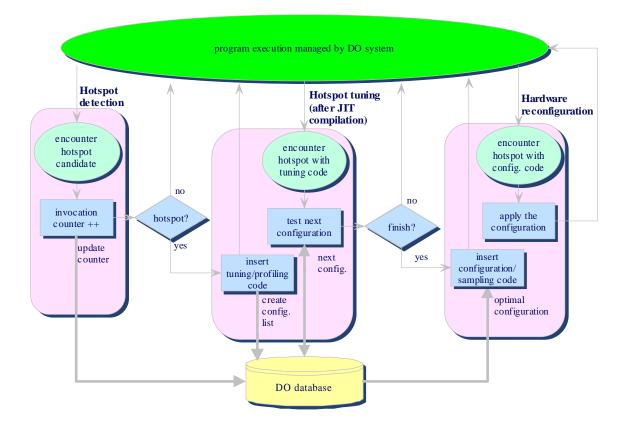

| Figure 2. Flowchart of the proposed hardware adaptation framework based on a         |

| dynamic optimization system                                                          |

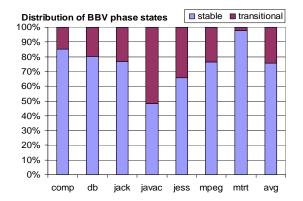

| Figure 3. Distribution of stable/transitional BBV phases of SPECjvm 98 benchmarks.   |

| (A phase is stable if it has two or more successive sampling intervals;              |

| otherwise it is an unstable phase)48                                                 |

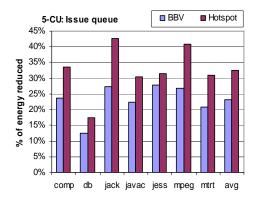

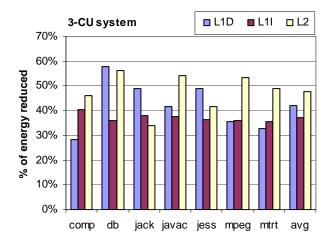

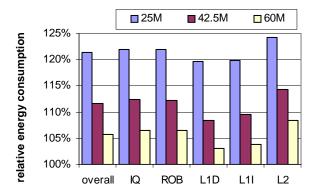

| Figure 4. Reduction in issue queue energy consumption by adapting the five           |

| configurable units (5% performance loss threshold)53                                 |

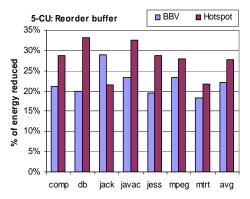

| Figure 5. Reduction in reorder buffer energy consumption by adapting the five        |

| configurable units (5% performance loss threshold)54                                 |

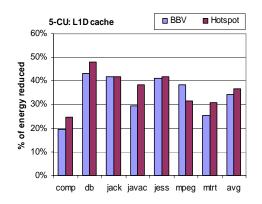

| Figure 6. Reduction in level-one data cache energy consumption by adapting the five  |

| configurable units (5% performance loss threshold)                                   |

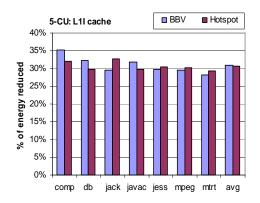

| Figure 7. Reduction in level-one instruction cache energy consumption by adapting    |

| the five configurable units (5% performance loss threshold)54                        |

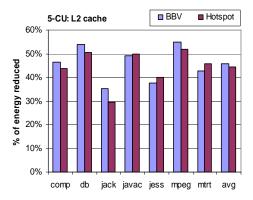

| Figure 8. Reduction in level-two cache energy consumption by adapting the five       |

| configurable units (5% performance loss threshold)55                                 |

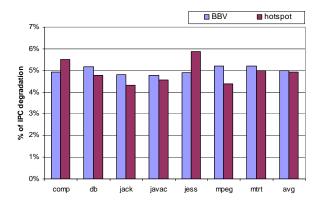

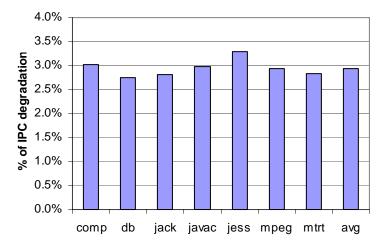

| Figure 9. Performance degradation due to the adaptation of the five configurable     |

| units55                                                                              |

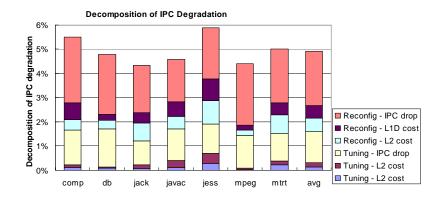

| Figure 10. Decomposition of the DO-based approach's IPC degradation56                |

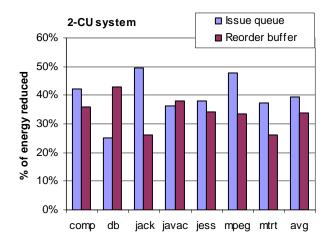

| Figure 11. Reduction in energy consumption by adapting issue queue and reorder       |

| buffer (2% performance loss threshold)                                               |

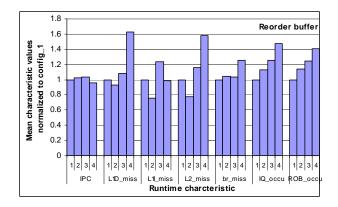

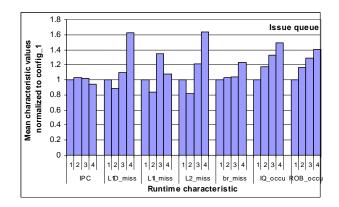

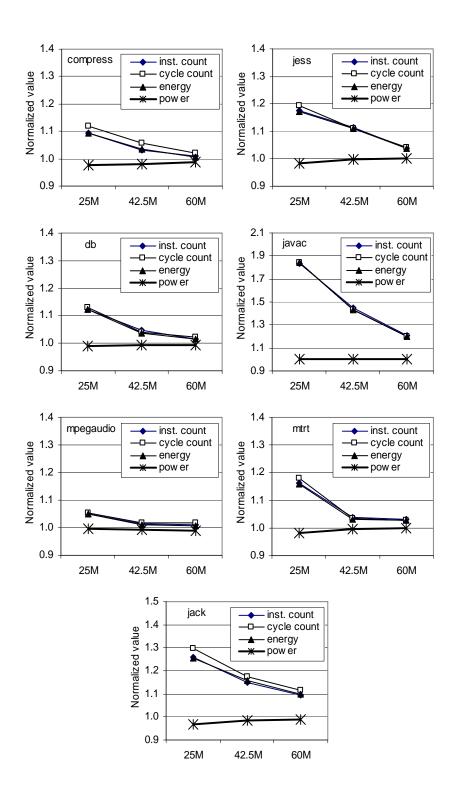

Figure 15. Runtime characteristics' impact on reorder buffer's adaptation. (1: 32entry ROB; 2: 64-entry ROB; 3: 96-entry ROB; 4: 128-entry ROB)70

- Figure 16. Runtime characteristics' impact on issue queue's adaptation. (1: 32-entry IQ; 2: 64-entry IQ; 3: 96-entry IQ; 4: 128-entry IQ)......70

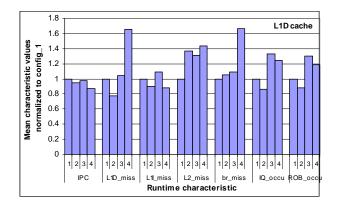

- Figure 17. Runtime characteristics' impact on L1D cache's adaptation. (1: 16K L1D cache; 2: 32K L1D cache; 3: 48K L1D cache; 4: 64K L1D cache) .71

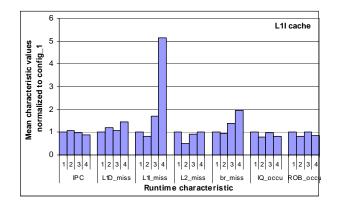

- Figure 18. Runtime characteristics' impact on L1I cache's adaptation. (1: 16K L1I cache; 2: 32K L1I cache; 3: 48K L1I cache; 4: 64K L1I cache) ......72

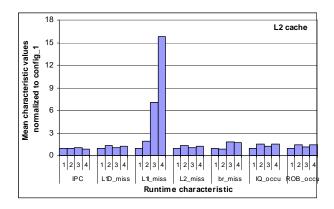

- Figure 19. Runtime characteristics' impact on L2 cache's adaptation. (1: 256K L2 cache; 2: 512K L2 cache; 3: 768K L2 cache; 4: 1M L2 cache) ......72

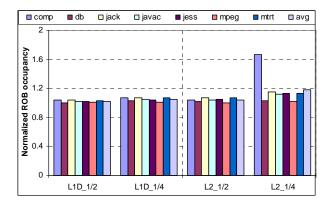

- Figure 20. Hardware units' interference on reorder buffer's adaptation......77

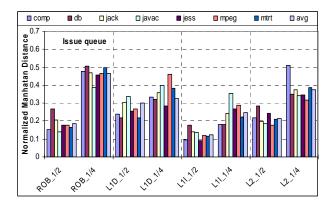

- Figure 22. Hardware units' interference on issue queue's adaptation......79

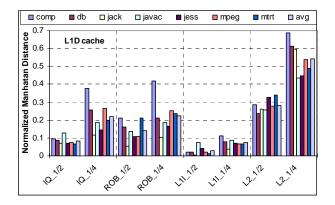

- Figure 23. Hardware units' interference on L1D cache's adaptation......80

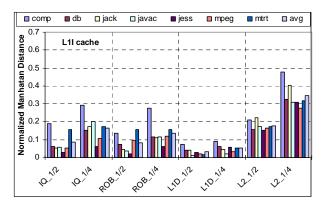

- Figure 24. Hardware units' interference on L1I cache's adaptation......80

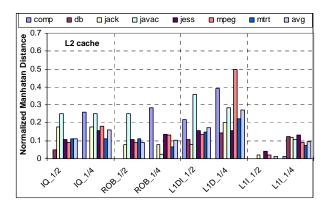

- Figure 25. Hardware units' interference on L2 cache's adaptation......81

| Figure 28. Reduction in reorder buffer energy reduction by using the tuning reduction |

|---------------------------------------------------------------------------------------|

| strategies                                                                            |

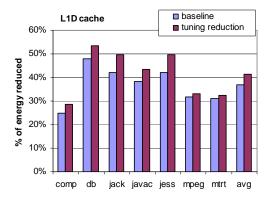

| Figure 29. Reduction in L1D cache energy reduction by using the tuning reduction      |

| strategies                                                                            |

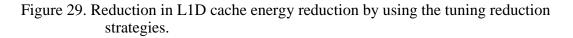

| Figure 30. Impact of the tuning-reduction strategies on L1I cache energy reduction.   |

|                                                                                       |

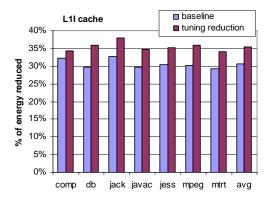

| Figure 31. Impact of the tuning-reduction strategies on L2 cache energy reduction.    |

|                                                                                       |

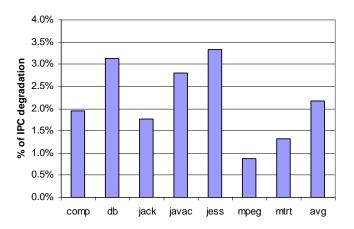

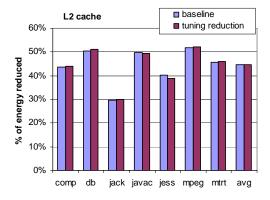

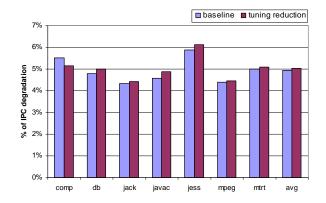

| Figure 32. Performance degradation due to the tuning reduction strategies             |

| Figure 33. Generalized tuning reduction algorithms for independent CUs91              |

| Figure 34. Generalized tuning reduction algorithms for CUs with positive              |

| interference                                                                          |

| Figure 35. Changes in performance, energy, and power due to garbage collection.103    |

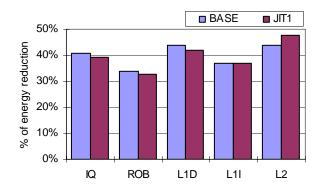

| Figure 36. Impact of JIT optimization on configurable unit energy reduction110        |

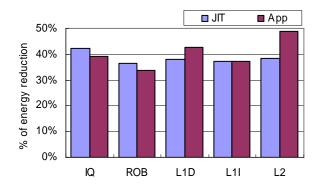

| Figure 37. Comparison of JIT optimizer and application on configurable unit energy    |

| reduction111                                                                          |

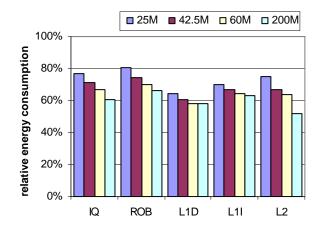

| Figure 38. Fixed size hardware units' energy consumption with small heaps as          |

| fractions of those with 200M heap. (The results are the same as the ones              |

| in the last column of Table 16)113                                                    |

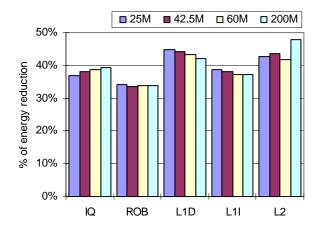

| Figure 39. Impact of garbage collection and hardware adaptation on configurable unit  |

| energy consumption114                                                                 |

| Figure 40. Impact of garbage collection on configurable unit energy reduction.115     |

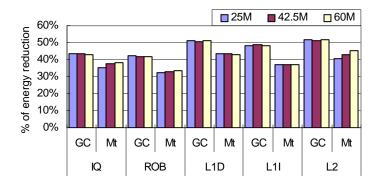

| Figure 41. Comparison of garbage collector and mutator on configurable unit energy    |

| reduction117                                                                          |

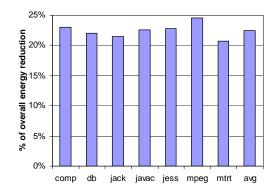

Figure 42. Percentage of a microprocessor's energy reduced by using the hardware adaptation framework to manage the five configurable units......120

### **Chapter 1. Introduction**

#### **1.1 MICROPROCESSOR ENERGY REDUCTION**

In the past several decades, advances in VLSI technologies and microarchitectural innovations have driven the continuous performance improvement of microprocessors. Today's high performance processors integrate millions of transistors and operate at Giga Hertz frequency. Despite performance achievement, processor architecture designs still face challenges. Specifically, the increasing power dissipation is one of the biggest concerns. Microprocessor power densities have been increasing substantially from one generation to the next, despite the reduced supply voltages and advanced processing technologies. High power densities of today's state-of-the art processors significantly affect circuit reliability, cooling issues, and package costs.

Meanwhile, the market for portable computation devices is growing quickly. In most embedded devices, the computing element accounts for a high portion of the overall energy consumption. Most embedded systems use batteries whose life is determined by the energy consumption of the embedded systems. Consequently, the interest in lowering the power and energy of a processor has grown dramatically over the past several years.

Various techniques are proposed to deal with this problem. First, low power VLSI devices and logic are designed to make significant contribution to power saving. In the circuit level, voltage scaling, low swing buses, and conditional clocking help reduce energy consumption enormously [34][85]. Power-aware compiler optimizations can also help alleviate the energy problem [32][77][83].

#### **1.2 ADAPTIVE MICROARCHITECTURES**

Adaptive microarchitectures are one of the commonly used techniques to dynamically identify configurations that are desirable from performance and power perspectives. By matching hardware configurations with changing program requirements, adaptive microarchitectures can reduce energy with minimal performance impact. With fixed size microarchitectural structures such as wide instruction window and large L1 caches, conventional microprocessors are designed to maximize performance for a range of applications. However, a program rarely fully utilizes every microarchitectural resource to achieve high performance. Hence, it is possible to reduce the sizes of those under-utilized microarchitectural resources for energy reduction with minimal performance impact. To achieve energy reduction, the hardware units must have multiple configurable units (CUs), such as issue queue, reorder buffer, caches, and branch predictors, have been proposed [1][7][27][36][63]. In this dissertation, the term *adaptive microarchitecture* indicates a microprocessor design with one or more such configurable hardware units.

Changing a hardware unit's setting at runtime usually incurs cycle-time *reconfiguration overhead*. For instance, to reduce a cache's size, dirty cache lines must be written back to lower memory hierarchy, which may take thousands of cycles [19]. Hence, a program's performance may be impaired by too frequent reconfigurations where reconfiguration exceeds the benefit gained by the reconfigurations. After a reconfiguration, the configuration should be utilized for a certain minimum time interval, called the CU's *reconfiguration interval*. Depending on its reconfiguration overhead, a configurable unit's reconfiguration interval can vary from thousands (e.g., issue queue [27]) to millions (e.g., caches [2]) of instructions/cycles.

Two important issues in hardware adaptation are *when* to adapt hardware resources and *which* configuration to adapt to. The first issue is addressed by program phase detection. By the definition of Sherwood et al. [75], a *phase* is a set of intervals within a program's execution that have similar behavior, regardless of temporal adjacency. Recent research in program runtime behavior confirms that programs execute as a series of phases with varying runtime characteristics and hardware requirements, while still having a fairly homogeneous behavior within a phase [19][20][75][76]. Phase boundaries are thus suitable points for resource reconfiguration. Previously proposed resource adaptation approaches rely on diverse hardware and software schemes to detect distinct program phases that are associated with either successive program sampling intervals or code positions.

The second issue of hardware adaptation, i.e., *which* configuration to adapt to, is addressed by the tuning strategy. Most prior hardware adaptation schemes use the same tuning strategy. Upon a phase change, this tuning strategy tests all hardware configurations and adapts to the *best* one (i.e., the most energy-efficient one that satisfies the performance constraint), and this procedure is called the phase's *tuning process*. The time taken by the tuning process is the phase's *tuning latency*, which is proportional to the number of configurations tested. For instance, the latency of tuning a fourconfiguration. On the other hand, in a multiple CU environment, the tuning process tests those CUs' combinational configurations.

#### **1.3 EFFICIENT MANAGEMENT OF MULTIPLE CONFIGURABLE UNITS**

In adaptive microarchitectures, efficient management of configurable units is vital for maximizing energy reduction. To achieve high energy reduction, an adaptive microarchitecture usually has multiple configurable units. Intuitively, in a multi-CU environment, changing one CU's configuration may affect the tuning decision of another CU. Hence, hardware units can hardly be adapted individually. This research is motivated by the importance on the efficient adaptation of multiple configurable units on overall energy reduction.

In a multi-CU environment, the straightforward tuning strategy of testing all combinatorial configurations results in a long tuning process. With this tuning strategy, the tuning latency is proportional to the total number of combinatorial configurations, which increases dramatically as more hardware units become configurable. For instance, a four-configuration CU needs only four tests, while adapting five four-configuration CUs needs 1024 tests. Figure 1 illustrates the tuning process of two four-configuration hardware units. Note that it is possible to reduce the tuning process by ruling out some unpromising configurations found via offline or online profiling.

Figure 1. Adaptation of two four-configuration hardware units. (Each pair of numbers is one combinational configuration, with the numbers indicating the two CUs' individual configurations.)

With multiple configurable units, using the straightforward tuning strategy of testing all combinatorial configurations significantly affects the efficiency of hardware adaptation. First, during the tuning process, the program mostly executes at configurations that yield less energy reduction or too much performance loss compared to the best one. Hence, the rapidly increased tuning latency impairs performance and energy reduction substantially. The performance is further impaired by the increasing tuning overhead that is proportional to the tuning latency. Finally, using the conventional tuning strategy implies that all CUs are adapted at the same pace, which must be chosen to accommodate the largest CU reconfiguration interval. Thus, reconfiguration opportunities are lost for low-overhead CUs. Consequently, it is imperative to find new tuning strategies that improve the adaptation of multiple CUs for better energy reduction.

#### **1.4 THESIS STATEMENT**

In adaptive microarchitectures, efficient management of the configurable units is vital for maximizing energy reduction. Utilizing a dynamic optimization system's inherent capabilities of detecting and optimizing hot spots, a hardware adaptation framework can efficiently manage multiple configurable units by adapting them at hot spot boundaries, and thus achieve much better energy reduction than conventional approaches.

#### **1.5 CONTRIBUTIONS**

This research makes multiple contributions to efficient adaptation of multiple configurable units for energy reduction.

The first contribution of this dissertation is that it demonstrates how a dynamic optimization (DO) system' inherent capabilities of detecting and optimizing hot spots can be synergistically employed for efficient management of adaptive microarchitectures. During the past decade, dynamic optimization systems have grown in popularity. *Dynamic optimization* is a software system's ability to dynamically translate/optimize one type of program code to another form, even in the same ISA. Examples of DO

systems include Transmeta CMS [18], IBM DAISY [24], HP Dynamo [8], Intel IA32EL [10], Java virtual machines [5][90], and Microsoft .NET's common language runtime [91]. To amortize the overhead of runtime translation and further improve performance, most DO systems apply high-cost high-quality optimizations only on frequently executed code sequences (hot spots). It has been shown that hot spots usually have stable runtime characteristics throughout program execution [84], and closely represent program behavior changes [36][56]. Therefore, DO systems are good platforms for adaptive computing environment management.

This dissertation presents a hardware adaptation framework for efficient management of multiple configurable units based on a generic dynamic optimization system. Exploiting the existing hot spot detection mechanism of the dynamic optimization system, the proposed framework adapts microarchitectural resources at hot spot boundaries.

The framework prunes the explosive tuning space of multiple CUs with two techniques. First, a technique, CU decoupling, decouples the adaptation of CUs with diverse adaptation cost. Program hot spots are usually of variable sizes and are nested. Smaller hot spots represent fine-grain phases nested within coarse-grain phases that appear as large hot spots. Intuitively, they closely represent hierarchical phase behavior. Thus, this framework automatically captures the hierarchical phase behavior by identifying nested hot spots. Utilizing this capability, the framework decouples the reconfiguration of different CUs by adjusting the granularity of adaptation based on each CU's reconfiguration cost. This *CU decoupling* strategy significantly reduces the tuning process, and achieves a better balance of benefit/overhead for each configurable hardware resource.

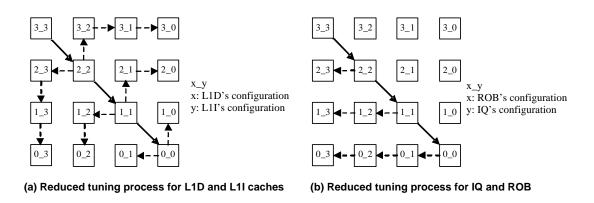

The second technique exploits the different types of interference between CUs' adaptation to prune the tuning space of multiple CUs. In a multi-CU environment, the interference between two CUs exists when one CU's configuration changes alter another CUs' adaptation decisions. For instance, some CUs, such as L1D and L1I caches, rarely interfere with each other, so they can be adapted in parallel. Furthermore, for CUs such as issue queue and reorder buffer, one's size reduction usually prompts the other to keep the same configuration or use a smaller one for energy reduction with minimal extra performance loss. With those types of interference, the search of the CUs' best configuration usually biases towards certain paths, and the tuning space can be pruned by testing only configurations in those paths. Differing with CU decoupling, those tuning reduction strategies are also effective for CUs with similar adaptation costs. Employing the two techniques, the framework manage multiple configurable units efficiently and achieve high energy reduction.

To demonstrate the usefulness and effectiveness of our framework, the proposed hardware adaptation framework is implemented using Jikes Research Virtual Machine [5] and Dynamic Simplescalar simulator [38]. Performance is evaluated on the SPECjvm98 benchmark suite [88]. Five configurable units are implemented: issue queue, reorder buffer, L1 instruction and data caches, and L2 cache. Previous research indicates that those five components dominate the energy consumption of a microprocessor [27]. Hence, improving those CUs' adaptation should considerably reduce the overall microprocessor energy consumption.

Another contribution of the work is the comprehensive investigation of the major adaptation-interfering factors in a multi-CU system, and the findings are applied to the design of new tuning-reduction strategies. The ultimate goal of a resource adaptation scheme is to achieve the lowest energy consumption and the best possible performance. If energy is the primary constraint, some performance losses may have to be tolerated. Similarly, if performance is the absolute goal, one may have to tolerate high power and energy. Abiding by program requirements and the performance budget, CUs' configurations are adjusted via their tuning processes to achieve the maximum overall saving. Hence. in multi-CU environment, energy а program's runtime characteristics/requirements and the interference imposed by other CUs' adaptation are the two major factors that affect a CU's tuning decision. In this research, those two adaptation-interfering factors are investigated. Following are several findings.

First, by qualitatively analyzing CUs' performance impact, two interference types between CUs are discovered: a) *positive*: one CU's size reduction relieves the performance pressure on the other one, and allows it to use the same or a smaller size; b) *negative*: one CU's size reduction increases the performance pressure on the other one, and prompts it to use a larger size. The interference between issue queue and reorder buffer are positive, which leads to the design of a tuning-reduction strategy for the two units.

Second, the interference of one CU's adaptation on another CU's tuning decisions varies by CUs. In general, high-overhead CUs are less sensitive to other units' interference than low-overhead CUs, which validates the efficiency of multi-grain adaptation employed by the DO-based hardware adaptation framework. There is extensive interference between issue queue and reorder buffer, while L1D and L1I caches have minimal mutual interference. Hence, the L1D and L1I caches can be adapted in parallel, disregarding each other's tuning.

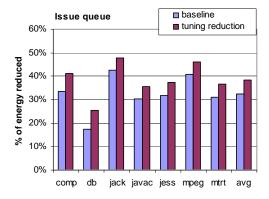

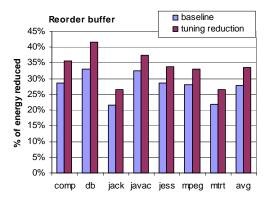

The interference analysis helps us design two tuning-reduction strategies. The first strategy reduces the latency of tuning L1D and L1I caches by adapting them in parallel. Exploiting the positive interference between the issue queue and the reorder

buffer, the second strategy reduces the tuning latency of those two CUs by testing only configurations that comply with the positive interference property. The CU decoupling technique decouples only the adaptation of CUs with diverse reconfiguration overheads, while those two tuning-reduction strategies reduce the adaptation latency of CUs with similar reconfiguration overheads. Hence, employing the tuning reduction strategies and the CU decoupling technique, the proposed framework significantly improves the energy efficiency of an adaptive microarchitecture.

Another contribution of this dissertation is the extensive study of the energy and power impact of two important dynamic optimization services, JIT optimization and garbage collection, on microprocessor energy consumption and hardware adaptation. By reducing instruction counts, JIT optimization significantly reduces a program's energy consumption, while garbage collection incurs runtime overhead that consumes more energy. Interestingly, both JIT optimization and garbage collection decrease the average power dissipated by a program. Detailed analysis reveals that both JIT optimizer and JIT optimized code dissipate less power than un-optimized code. On the other hand, the garbage collector dissipates less power than the mutator, but it rarely affects the mutator's average power.

This research also reveals that DO systems interfere with hardware adaptation. Both JIT optimization and garbage collection alter programs' behavior and runtime requirements. In adaptive microarchitectures, such changes of runtime requirements can considerably affect the adaptation of configurable hardware units, and eventually influence the overall energy consumption. The adaptation preferences of configurable units on the JIT optimizer and the garbage collector are also studied, demonstrating that the units' adaptation decisions on the application code and the dynamic optimization services can differ substantially. The insights gained in this research point to novel techniques that can further reduce microprocessor energy consumption.

#### **1.6 ORGANIZATION**

The remainder of the dissertation is organized as follows:

Chapter 2 presents the background and related work on hardware resource adaptation, dynamic optimization, and energy and power impact of compiler optimizations. Chapter 3 introduces the proposed hardware adaptation framework. Chapter 4 discusses the experimental methodology used in this research. Chapter 5 evaluates the framework and compares it against one of the best prior resource adaptation schemes on managing multiple configurable units. Chapter 6 examines how runtime program requirements, in terms of measurable characteristics, affect CUs' adaptation decisions. Interference imposed by the adaptation of CUs on other CUs' tuning decisions is also studied in this chapter. Dynamic optimization and garbage collection are two of the major services in many dynamic optimization systems that assist program execution. Chapter 7 analyzes the impact of those two dynamic optimization services on microprocessor energy consumption and hardware adaptation. Chapter 8 concludes the dissertation by summarizing the contributions and suggesting future directions.

### **Chapter 2. Background and Related Work**

This chapter presents the background and the related work on hardware optimization systems, and compiler adaptation, dynamic optimizations for microprocessor energy reduction. First, various configurable units and the terms reconfiguration overheads and intervals of CUs that are used throughout the dissertation are introduced. Most resource adaptation schemes have two components: a phase detection mechanism that identifies when to adapt hardware resources, and a tuning strategy to identify which units to configure and how to configure the units. Section 2.2 describes previously proposed phase detection mechanisms, and Section 2.3 introduces the commonly used tuning strategy and identifies its key limitations on managing multiple configurable units. Several exemplary dynamic optimization systems are presented in Section 2.4. All of those dynamic optimizations systems detect and optimize hot spots to minimize dynamic optimization cost. The impact of compiler optimizations on microprocessor power dissipation and energy reduction is discussed in Section 2.5.

#### **2.1 CONFIGURABLE HARDWARE UNITS**

Configurable hardware units are proposed to reduce energy consumed by those units with minimal performance impact. Changing a hardware unit's setting at runtime usually incurs cycle-time *reconfiguration overhead*. For instance, to reduce a cache's size, dirty cache lines must be written back to lower memory hierarchy, which may take thousands of cycles [19]. Hence, a program's performance may be impaired by too frequent reconfigurations where reconfiguration overhead overcomes the benefit gained by the reconfigurations. After a reconfiguration, the configuration should be utilized for a certain minimum time interval, called the CU's *reconfiguration interval*. Depending on its reconfiguration overhead, a configurable unit's reconfiguration interval can vary from thousands (e.g., issue queue [27]) to millions (e.g., caches [2]) of instructions or cycles. The following subsections studies the following configurable units: issue queue, reorder buffer, caches, branch predictors, and filter cache etc.

#### 2.1.1 Issue queue

In out-of-order superscalar microprocessors, multiple instructions are dynamically reordered and issued to functional units in their data ready order rather than their original program order to achieve high performance. Two hardware units that facilitate dynamic instruction scheduling are issue queue and reorder buffer. Due to their highly associative nature, they are among the most power-hungry and time-critical components in a modern processor. Hence, numerous previous efforts focus on reducing the energy consumption of issue queue and reorder buffer by adjusting their sizes dynamically, or by utilizing low-complexity, low-power alternative ones when suitable.

Many issue queue energy reduction schemes dynamically adjust issue queue sizes to match program requirements for energy saving. To estimate program computational demand and to guide adaptation, they usually sample measurable metrics such as IPC or issue queue occupancy. Folegnani et al. [27] propose an energy effective issue logic design, which saves energy by reducing the issue queue size dynamically, as well as avoiding waking up empty issue queue entries and ready operands. Bahar et al. [6] adapt multiple processor resources, including the issue queue, by balancing the pipeline width with program requirements at runtime. Similar designs are discussed in several other works [1][63][65] as well.

Several other schemes reduce the energy consumption of issue queue by providing low complexity, low power alternatives. Those issue queues can be used solely, or combined with the conventional out-of-order, high power consumption issue queue for better energy saving. Using the low-power issue queues when program has less available ILP can save energy with minimal or even beneficial performance impact. Canal et al. [15] propose two low-complexity issue queues. The first issue queue design, first-use issue scheme, replaces the conventional out-of-order issue queue with several inorder queues by utilizing the fact that most register values are read at most once. The second scheme, distant issue logic, tries to determine instruction execution order in the decode stage, thus simplifying complex dynamic scheduler used in conventional issue logic. It provides extra hardware to hold instructions that wait for memory accesses. Abella et al. [3] present a low-complexity distributed issue queue design that classifies instructions and dispatches them into a set of FIFO queues depending on their data dependences.

Several other efforts try to simplify the issue queue design by using a less aggressive hardware instruction scheduler. Ernst et al. [25] implement the simple hardware Cyclone scheduler that schedules instructions by predicting the ready latencies of the instructions' operands. The Cyclone instruction queue schedules predicted instructions via a network of locally synchronized datapaths. To ensure correct program execution in the presence of latency and dependence speculation, the Cyclone scheduler incorporates a selective replay mechanism that overloads the register forwarding infrastructure to re-execute only those instructions dependent on incorrectly scheduled instructions. A similar scheme is proposed by Michaud et al. [58].

#### 2.1.2 Reorder buffer

As one of the key datapath structures in modern superscalar, out-of-order processors, the reorder buffer (ROB) maintains the program order and precise states of instructions when them execute out of order. In some microarchitectures, such as the Intel P6, the physical registers are implemented as slots within the ROB entries, which, combined with the large number of ROB ports, contribute a significant percentage to the

overall chip power dissipation [27]. Hence, it is important to reduce the ROB power consumption with minimal performance loss. Several prior efforts in the area propose to dynamically adjust the size of ROB for better energy efficiency [6][42]. Besides the reorder buffer, Wu et al. [83] also adjust the fetch width of the microprocessor dynamically.

Kucuk et al. [47] exploit the observation that in a typical superscalar datapath, almost all of the source operand values are obtained either through data forwarding of the recently generated results or from the reads of the committed register values. Only a small percentage of the operands need to be read from the ROB; delaying such reads have little impact on the overall performance. This allows the ROB ports for reading the source operands at the time of dispatch to be completely eliminated with little performance loss. Another paper [46] extends the scheme by implementing a ROB with distributed queues. Each ROB queue serves a single functional unit, with a single write port instead of multiple ones needed by a centralized implementation.

#### 2.1.3 Cache hierarchy

Due to their large sizes, on-chip caches contribute much to a microprocessor's power dissipation and energy consumption. Various adaptable cache schemes have been proposed in past research. Some of them disable parts of cache ways or cache lines, or access only the cache ways that are most likely to hit. Cache line width and hierarchy can be adjusted to adapt to program requirements.

Albonesi [2] proposes to a technique, called *selective cache ways*, to reduce cache energy consumption by dynamically disabling a subset of cache ways in a set associative cache. Selective cache ways exploits the fact that large on-chip caches are often partitioned into multiple subarrays to reduce the long word and/or bitline delays of a single large cache array. Hence, only minor changes, e.g., gating hardware and a control

register, are required to implement selective cache ways in a conventional cache. A similar adaptive complexity-adaptive cache hierarchy is proposed [1] as a part of the so-called complexity adaptive processors.

During a cache access, usually both the tag and data arrays are activated. A cache in the phased mode [31] is a set associative cache where an access first activates only the tags. If there is a match, only the matching data array is subsequently activated, reducing the amount of bitline activity and sense amplification in the data array. Consequently, a phased cache saves energy at the cost of extra delay. Min et al. [59] present a low power cache system that compares tags in two phases. The first phase determines the data ways that the memory access falls into, which is then verified by the second phase. With those two phases, most activities in accessing a conventional cache tag can be avoided, and thus achieve energy saving. The approaches proposed by Powell et al. [64] predict the matching ways and probes only the predicted ways and not all the ways to achieve energy saving. A similar approach is proposed by Zhang et al. [86], in which a small way-halting cache stores partial tags and is accessed in parallel with set-index decoding. Thus, the ways with mismatching tags can be disabled during the cache assess for energy saving.

Kaxiras et al. [45] exploit the fact that cache lines are usually not accessed for a long period before they are evicted. Hence, tuning off the cache lines during the dead period can reduce power leakage, without introducing any additional cache misses that hurt performance. The paper proposes several policies for determining when to turn a cache line off. Based on the same principle, the drowsy cache [26] reduces cache leakage by exploiting the fact that during a fixed period of time, only a small subset of cache lines are accessed. Hence, inactive cache lines can transfer to a low-power drowsy mode with minimal performance loss.

Balasubramonian et al. [9] propose a cache hierarchy reconfiguration scheme that behaves as a virtual two-level, physical one-level non-inclusive cache hierarchy. In the scheme, multiple levels of the cache hierarchy share a large cache. The boundaries between L1 and L2 caches, and thus their sizes, are adapted at runtime by monitoring phase changes using miss rates and branch frequencies. The scheme is also applicable to TLBs. Based on the same principle, Ranganathan et al. [68] propose a reconfigurable cache in which a portion of the cache could be used for another function, such as an instruction reuse buffer. Veidenbaum et al. [82] describe an adaptive cache design in which cache line size is dynamically adapted based on program requirements monitored by hardware, although it aims at improving cache miss rate, not reducing energy consumption.

The Filter cache [48] is proposed to reduce the power consumption of an L1 instruction cache. The Filter cache is a small, direct-mapped cache that resides between processor core and the L1 instruction cache. If it is deactivated, instructions are fetched directly from the L1 instruction cache; otherwise, the processor checks the filter cache first. Filter cache hits save energy and improve performance, while filter cache misses consume more energy and lose performance.

#### 2.1.4 Other hardware units

Branch prediction is essential for increasing instruction-level parallelism. However, a large amount of unnecessary work results from wrong-path instructions entering the pipeline due to misprediction. Previous work [61] shows that in general, such speculation cost is worthwhile. Yet, it is still possible to improve the energy efficiency of branch prediction without hurting its accuracy. The work also proposes two techniques, banking and the prediction probe detector, to reduce the power dissipation of branch predictors. Banking allows partial activation of the branch predictor during a predictor access. The prediction probe detector uses pre-decode bits to entirely eliminate unnecessary predictor and branch target buffer accesses. Manne et al. [53] use confidence estimation to gate the execution of branches that are most likely to be mispredicted, and thus save energy.

Wide-issue processors typically have many functional units (FUs). Since few applications need all the FUs all the time, processors typically clock-gate unused FUs, which can significantly reduce the energy consumed by FUs. However, performance will be impaired when program requires more FUs than available ones. This scheme is used to reduce microprocessor energy consumption [6][36].

Besides turning off whole or part of hardware resources, it is also possible to scale down the voltage and frequency of processor core and DRAM array for energy saving. Dynamic energy is proportional to the square of the supply voltage, while dynamic power is proportional to the frequency and to the square of the voltage. Hence, reducing both the voltage and the frequency reduces energy, and is thus widely used in modern microprocessors [39]. Lowering the voltage of DRAM array can be conducted by changing the reference voltage used in an on-chip voltage converter according to the outputs of a detector [43].

#### **2.2 PROGRAM PHASE DETECTION**

Recent research in program runtime behavior confirms that programs execute as a series of phases, where each phase may be very different from the others, while still having a fairly homogeneous behavior within a phase [19][20][75][76]. By the definition of Sherwood et al. [75], a *phase* is a set of intervals within a program's execution that have similar behavior, regardless of temporal adjacency. Accurate and timely identification of program phases is essential for improving the effectiveness of adaptation. For instance, in systems that contain CUs with large reconfiguration

overheads, recurring phases may reuse configuration information to avoid repeated tunings to improve performance.

Balasubramonian et al. [9] use a conditional branch counter to detect program phase changes. The counter keeps track of the number of dynamic conditional branches executed over a fixed execution interval. Phase changes are detected when the difference in branch counts of consecutive intervals exceeds a threshold. Their scheme does not use a fixed threshold. Rather, the detection strategy dynamically varies the threshold throughout the execution of the program.

Sherwood et al. [76] propose to use an array of hardware counters, called basic block vector (BBV), to capture and classify phase-based program behavior on large time scales. This scheme is an online variant of the offline phase analysis and profiling tool SimPoint [74]. BBVs keep track of execution frequencies of basic blocks touched in a particular execution interval. Phase changes are detected when the Manhattan distance between consecutive BBVs exceeds a preset threshold. The paper demonstrates that sampling intervals of the same phase are homogeneous over multiple performance metrics. Program phases are usually hierarchical, i.e., they are of variable lengths and nested. Lau et al. [49] extend the SimPoint tool to detect hierarchical phases by using k-means clustering to group intervals with similar BBVs into clusters. However, the technique is complex and cannot be performed at runtime. Hence, it is hard to apply it to the online BBV phase detection technique.

Dhodapkar et al. [19] propose to use instruction working set signatures, i.e., highly compressed working set representations, to identify program phase behavior. The rationale is that as program phase behavior changes, the phases' instruction work sets should change also. Hence, by identifying the working set changes, one can detect phase changes and trigger hardware re-tuning. The working set signature is an n-bit vector formed by mapping addresses of cache line accesses into the vector buckets using a randomizing hash function.

All of the above phase change detection schemes can classify intervals with similar characteristics into phases, and allows hardware reconfiguration techniques to adapt for each phase. This is mainly due to their use of microarchitecture independent phase detection metrics. Dhodapkar et al. [20] compare the three phase detection techniques in terms of sensitivity to phase changes and false positive, phase stability and length. It finds out that the BBV technique performs better than other techniques.

Several other phase detection schemes identify phases using microarchitecture dependent metrics such as IPC [27] and occupancy [63]. One deficiency of such schemes is that the characteristics used to trigger hardware retuning are microarchitecture-dependent, and are affected by configuration changes conducted by the schemes. To minimize such interference, the configurable units have to be adapted to their maximum sizes once in a while.

The above phase detection schemes are all temporal ones, in that phases consist of sampling intervals with fixed or varying sizes. In temporal approaches, phases can be classified into stable and transitional ones [20]. A phase is *stable* if it lasts two or more successive sampling intervals; otherwise, it is *transitional*. Transitional phases have short lifetimes, rarely recur, and are thus difficult to tune. Recognizing only stable phases can improve the phase detection hardware utilization and increase phase detection accuracy considerably [20]. Lau et al. [50] propose to filter out transitional phases also.

In temporal approaches, a phase change cannot be identified immediately. It can only be detected after the phase change lasts one or more sampling intervals, which is called the identification latency. Recurring phases in those temporal approaches incur phase identification latencies, regardless the length of program execution. Recurring phase identification latencies can be reduced by next phase detection mechanisms [50][76], which predict what the next phase will be and when it will occur. However, incorrect predictions cause unnecessary or wrong adaptation and subsequent rollback of hardware configurations, thus affecting performance considerably. Hence, high prediction accuracy is imperative for such mechanisms. Based on the BBV phase detection technique, Sherwood et al. [76] propose two phase prediction mechanisms, Markov and Run-length-encoding Markov predictors. Lau et al. [50] also examine the issue, and propose several improved phase prediction schemes using hybrid predictors and confidence. Nevertheless, it is hard to accurately predict phase changes. Hence, current complex predictors usually provide marginal benefits over no prediction [50].

Differing from temporal approaches that detect phases at successive sampling intervals, the positional approach [36][83] captures phase changes at certain positions such as procedure boundaries, relying on the observation that program phase behavior is closely associated with program structures. Since it is hard to find procedure calls that start new phases by hardware at runtime, the positional approach simply adapts at boundaries of large procedures [36]. It has been shown that phase detection techniques based on large procedure boundaries do not perform as well as those based on the temporal approaches due to their inability to adapt to changes within the procedures [20].

Recently, Shen et al. [72] propose to construct memory phases based on memory localities. The scheme first profiles program execution using variable-distance sampling, wavelet filtering, and best phase partition via tracing a training input. It then identifies the memory phase hierarchy through grammar analysis. Finally, the phase information is inserted into program code by a static compiler. The technique is mainly used for cache adaptation. Its efficiency on adapting other hardware units is yet to be proven. Iyer et al. [42] propose a microarchitecture-level power management scheme to detect program phase changes and triggers the adaptation of multiple hardware resources. It uses a hardware profiling scheme to identify tightly coupled regions of code and a hardware-based power estimation method to judge the power requirements for each region of code and scale or resize resources at runtime depending on these estimates. The hardware hot spot detection scheme is based on the work of Merten et al. [56]. However, the limited scope of hot spot detection hardware and its frequent flushes indicate that the scheme can only detect small, locally-hot code regions, and is unable to detect large, global hot spots.

#### **2.3 RESOURCE ADAPTATION STRATEGIES**

The tuning strategies used in previous resource adaptation schemes [9][36][37][42] are similar in nature. In general, after a phase is found, the tuning strategy tests different configurations of a CU in successive sampling intervals (the temporal approaches), or successive invocations of the same code (the positional approach). It tests the least energy efficient configuration first. The tuning process completes when all the configurations have been tested. The most energy efficient configuration that satisfies the performance constraint is then selected for the phase. The tuning latency, the time taken to find the most energy-efficient configuration, is the number of sampling intervals required to test all the configurations.

With multiple configurable units, using the straightforward tuning strategy of testing all combinatorial configurations significantly affects the efficiency of hardware adaptation. First, during the tuning process, the program mostly executes at configurations that yield less energy reduction or too much performance loss compared to the best one. Hence, the exponentially increased tuning latency impairs performance and energy reduction substantially. Furthermore, the performance is also impaired by the

increasing tuning overhead that is proportional to the tuning latency. Finally, using the conventional tuning strategy implies that all CUs are adapted at the same pace, which must be chosen to accommodate the largest CU reconfiguration intervals. Reconfiguration opportunities are thus lost for low-overhead CUs. Consequently, resource adaptation schemes always prefer short tuning processes to long ones.

Several prior efforts aim at efficient adaptation of multiple configurable units. Ponomarev et al. [63] propose a scheme that periodically samples occupancies of data path buffers to adapt them independently. Dropsho et al. [21] minimizes the overhead of managing multiple configurable units by using local information, such as a cache's LRU states and a buffer's occupancy statistics, to guide each configurable unit's tuning decision. The paper notes that configurations of interdependent CUs are coupled, and cannot be recognized by local tuning strategy. Hence, a global tuning strategy might exploit the coupled effects for more energy reduction. The two hardware adaptation schemes are extended in a scheme that trades off clock frequencies with hardware structure sizes to achieve high throughput [22]. For multimedia applications, Sasanka et al. [73] propose multiple local hardware adaptation schemes to exploit intra-frame execution variability. Those local schemes are integrated with the global scheme, exploiting per-frame execution slack, to achieve better overall energy reduction.

#### 2.4 DYNAMIC OPTIMIZATION SYSTEMS

During the past decade, dynamic optimization (DO) systems have grown in popularity. Dynamic optimization is a software system's ability to dynamically translate/optimize one type of program code to another form, even in the same ISA. Examples of DO systems include IBM DAISY [24], Transmeta CMS [18], HP Dynamo [8], Intel IA32EL [10], Java virtual machines [5][90], and Microsoft .NET's common language runtime [91]. Some of those systems are full system emulators that emulate a

whole system, and execute under the operating system. The others execute at the user space and above the operating system.

Dynamic optimization systems provide several hardware and software engineering advantages over statically compiled binaries, including flexible hardware design, portable program representations, some safety guarantees, build-in automatic memory and thread management. This section reviews five typical dynamic optimization systems.

#### **2.4.1 Jikes Research Virtual Machine (RVM)**

Jikes RVM [5] is a research Java virtual machine (JVM) developed in IBM T. J. Watson Center, and is the first Java virtual machine written in Java. In addition to providing a high-level strongly-typed development environment, this design decision allows the optimization techniques to apply not only to application code, but also to the JVM itself.

Jikes RVM employs a compile-only strategy. It includes two, baseline and optimizing, compilers. The baseline compiler translates bytecodes directly into native code without any optimization. It is also used to validate the optimizing compiler. The optimizing compiler first translates bytecodes into an intermediate representation (IR). It then optimizes the IR before translating it into native code. The optimizing compiler of Jikes RVM has three levels of optimizations (JIT0, JIT1, and JIT2), each one consisting of its own group of optimizations as well as the optimizations that belong to lower levels. The lower two levels (JJT0 and JIT2) perform optimizations that are fast and high-payoff. JIT0 performs inlining and register allocation. JIT1 contains optimizations, such as such as common sub-expression elimination, copy and constant propagation, and dead-code elimination. JIT2 contains more expensive ones, such as those based on static single assignment (SSA) form.

Jikes RVM's adaptive optimization system is responsible for choosing the right compilation level for a given method. It uses a low-overhead sampling method to detect program hot spots. Approximately every 10 milliseconds, Jikes RVM increments a counter associated with the currently active procedure. For all methods that have been sampled, Jikes uses a cost/benefit model to determine whether it is profitable to recompile the method, and if so, what level of optimization to use.

### 2.4.2 Other dynamic optimization systems

The IBM DAISY system [24] emulates a PowerPC processor and executes on a DAISY VLIW processor. When the system powers up, the DAISY code is executed to initialize itself and the system. Then, it begins PowerPC emulation by interpreting all PowerPC instructions belonging to PowerPC firmware, AIX operating system, or user applications. It uses a counter based scheme to detect hot spots and translate newly detected hot spots into native VLIW code. Hence, when the hot spot is encountered again, its native VLIW code is executed. During the JIT compilation, DAISY performs a variety of optimizations including ILP scheduling with data and control speculation, loop unrolling, alias analysis, load-store telescoping, copy propagation, combining, unification, and limited dead code elimination.

The Transmeta Crusoe [18] emulates an x86 system on a VLIW chip specifically designed to support binary translation for x86. It is similar to IBM DAISY in that they are both full system emulators. However, Crusoe is aimed at low power and mobile applications, with narrow issue width and smaller memory budgets than IBM DAISY. Crusoe maintains a shadow copy of the x86 portion of its register set, and a gated store buffer to efficiently recover from exceptions. Hence, within the scope of a group, instructions can be arbitrarily reordered or deleted. Thus, Crusoe can perform optimizations such as strength reduction and aggressive dead code elimination. In other ways, Crusoe optimization is similar to that of DAISY. Code is first interpreted and profiled. If a fragment turns out to be frequently executed (more than 50 times), it is translated to native Crusoe instructions.

HP Dynamo [8] is a dynamic optimization system that takes PA-RISC code and produces optimized PA-RISC code. Implemented entirely in software, HP Dynamo runs above the HPUS operating system. Its operation is transparent: no preparatory compiler phase or programmer assistance is required. Dynamo improves execution time on some SPEC benchmarks by up to 22% and by an average of more than 10%. Initially, Dynamo interprets the instruction stream until a hot instruction sequence (trace) is identified. To identify hot traces, Dynamo associates counters with loop headers. If the counter exceeds a preset threshold value, the instruction starts a hot trace. Dynamo records the sequence of instruction as they are being interpreted until an end-of-trace condition is reached. At that point, Dynamo generates an optimized version of the hot trace (fragment) into a software code cache. Subsequent encounters of the hot trace will invoke the optimized fragment in the fragment cache. Due to the significant overheads of operating at runtime, Dynamo has to maximize the impact of any optimizations that it performs. Dynamo primarily looks for performance opportunities such as redundancies that cross static program boundaries. Another performance opportunity is instruction cache utilization since a dynamically contiguous sequence of frequently executing instructions may often be statically non-contiguous in the application binary.

IA-32 Execution Layer (EL) [10] is a two-phase dynamic translator that executes IA-32 application on Itanium-based systems. Similar to HP Dynamo, it executes only applications, and is available on both MS Windows and Linux operating systems. Initially, basic blocks are translated by IA-32 EL by using prepared translation template, and are instrumented to collect information for the second phase. When a block is found to be invoked enough times, the subsequent blocks executed are selected as a hyperblock. Based on the information collected during the first phase, various optimizations are applied on the hyperblock to improve its performance.

### 2.4.3 Hot spot detection and optimization

Dynamic optimization systems usually focus costly optimizations on program hot spots to reduce runtime compilation overhead and improve performance. Program *hot spots* are frequently executed code sequences, such as procedures [5] or basic block groups [8][18][24]. To amortize the overhead of runtime translation and further improve performance, most DO systems apply high-cost, high-payoff optimizations only to hot spots. A DO system usually includes the following steps to detect and optimize hot spots. Initially, a program code block is interpreted [8][18][24] or quickly translated and instrumented [5]. The execution frequency information of the code block is then gathered by the interpreter or the profiling code instrumented at hot spot boundaries, and saved in the code block's corresponding entry in the DO database that stores runtime profiling information for the DO system. The information is then examined to find frequently executed code blocks as hot spots, and advanced optimizations are applied on them.

The hot spot detection mechanism in the DO system can be used directly for phase identification. Wu et al. [84] indicate that the runtime characteristics of hot spots are usually stable throughout program execution. Huang et al. [36] and Merten et al. [56] observe that program phase behavior is closely related with hot spot invocations. Hence, tuning and reconfiguring CUs at hot spot boundaries should accurately adapt to program changes.

#### **2.5 POWER-AWARE COMPILER OPTIMIZATIONS**

With the importance of energy reduction, previous work examines the impact of static compiler optimizations on program energy consumption and power dissipation. Kandemir et al. [41] investigate the influence of several compiler optimizations, such as linear loop transformations, blocking, loop unrolling and loop fusion, on programs' energy consumption. They find that those optimizations usually reduce the memory energy consumption at the cost of rising core energy consumption. Valluri et al. [80] note that compiler optimizations for locality and instruction counts usually optimize program energy consumption, while optimizations improving ILP increase average power dissipation. In their study of Pentium 4 power consumption, Seng et al. [71] note that compiler optimizations affect programs' energy consumption mainly by reducing their execution time. Chakrapani et al. [16] examine the interaction between compiler optimizations and processor components, and draw similar observations as Valluri [80].

Power-aware compiler optimizations improve program energy consumption and power dissipation. Simunic et al. [77] perform several compilation optimizations, including loop merging, unrolling, software pipelining, loop invariant extraction to optimize the performance and energy consumption of a MPEGAUDIO video decoder in an embedded system, with the assistance of profiling information. Software pipelining is used by Yang et al. [85] in a power-aware instruction scheduling scheme to reduce power variation throughout program execution.

Compiler optimizations can also assist hardware energy reduction proposals. Valluri et al. [81] use the compiler to assist instruction scheduling, thus achieving low power, low-complexity instruction issue. Compared with run-time scheduling, compiletime scheduling features fast and simple hardware, but at the expense of conservative schedules [32]. The paper implements a compile-time analyzer to identify basic blocks free of memory misses, false-dependences, or unresolved alias edges, and schedules them statically. This issue queue design includes two types of queues, a FIFO queue for statically scheduled instructions and a fully associative queue for instructions requiring dynamically scheduling. The scheme consumes less energy than the conventional issue queue since the fully associative queue is much smaller, and has a smaller issue width than the conventional one.

A compiler-directed strategy [34] identifies non-critical program code regions, and dynamic voltage and frequency can be scaled down on those regions for energy reduction. The compiler can also detect program regions that do not use certain hardware components, e.g., hard disk, for certain long enough periods so that the hardware components can be in hibernation for energy reduction [32].

All of the above research focuses on static compiler optimizations. Recently, Wu et al. [83] propose a lightweight dynamic compilation framework for dynamic voltage and frequency scaling (DVFS). This framework does not include the JIT optimization or garbage collection capability. It detects hot code regions that are memory-bound, and inserts DVFS mode set instructions at the boundaries of those regions so that they can be executed in energy-efficient modes.

# Chapter 3. Hardware Adaptation Framework based on Dynamic Optimization

In the presence of multiple CUs, especially those that have diverse reconfiguration overheads, existing resource adaptation schemes have considerable limitations. To efficiently manage multiple CUs, a hardware adaptation framework based on a generic dynamic optimization system is developed and presented in this chapter. Although the idea of integrating hardware adaptation with a virtual machine is not new [19], to the best of our knowledge, this research is the first one that utilizes a DO system's inherent capabilities of detecting and optimizing hot spots to efficiently manage multiple configurable hardware resources.

Figure 2 shows the flowchart of the proposed hardware adaptation framework. Thin lines indicate program control flows, and thick lines represent data flows. Three main tasks are performed. Initially, the DO system monitors program execution and detects hot spots. After a hot spot is detected and JIT optimized, the DO system inserts tuning code at hot spot boundaries to identify the most energy-efficient hardware configuration for the hot spot during its subsequent invocations. After the tuning finishes, the JIT compiler replaces the tuning code with the code that automatically adapts to the hot spot's most energy-efficient configuration whenever it is invoked. The details of the framework are explained in the following sections.

Figure 2. Flowchart of the proposed hardware adaptation framework based on a dynamic optimization system.

### **3.1 HOT SPOT DETECTION**

Program *hot spots* are frequently executed code sequences, such as procedures [5] or basic block groups [8][18][24]. To amortize the overhead of runtime translation and further improve performance, most DO systems apply high-cost, high-payoff optimizations only to hot spots. A DO system usually includes the following steps to detect and optimize hot spots. Initially, a program code block is interpreted [8][18][24] or quickly translated and instrumented [5]. The execution frequency information of the code block is then gathered by the interpreter or the profiling code instrumented at hot spot boundaries, and saved in the code block's corresponding entry in the DO database that

stores runtime profiling information for the DO system. The information is then examined to find frequently executed code blocks as hot spots, and advanced optimizations are applied on them.

The hot spot detection mechanism in the DO system can be used directly for phase identification. Wu et al. [84] indicate that the runtime characteristics of hot spots are usually stable throughout program execution. Huang et al. [36] and Merten et al. [56] observe that program phase behavior is closely related to hot spot invocations. Hence, tuning and reconfiguring CUs at hot spot boundaries should accurately adapt to program changes.

#### **3.2 CU DECOUPLING AND HOT SPOT TUNING**

After a hot spot is detected, the CU decoupling technique is applied to the hot spot to reduce its tuning process.

#### **3.2.1 CU decoupling**