Copyright

by

Yashwant Marathe

2018

# The Thesis Committee for Yashwant Marathe Certifies that this is the approved version of the following thesis:

# Improving Virtual Memory Performance in Virtualized Environments

| APPROVED BY                |

|----------------------------|

| SUPERVISING COMMITTEE:     |

|                            |

| Lizy K. John, Supervisor   |

|                            |

| Nagendra Gulur Dwarakanath |

## Improving Virtual Memory Performance in Virtualized Environments

by

## Yashwant Marathe

#### Thesis

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

Master of Science in Engineering

The University of Texas at Austin  ${\bf August~2018}$

### **Abstract**

## Improving Virtual Memory Performance in Virtualized Environments

Yashwant Marathe, M.S.E.

The University of Texas at Austin, 2018

Supervisor: Lizy K. John

Virtual Memory is a major system performance bottleneck in virtualized environments. In addition to expensive address translations, frequent virtual machine context switches are common in virtualized environments, resulting in increased TLB miss rates, subsequent expensive page walks and data cache contention due to incoming page table entries evicting useful data. Orthogonally, translation coherence, which is currently an expensive operation implemented in software, can consume up to 50% of the runtime of an application executing on the guest. To improve the performance of virtual memory in virtualized environments, two solutions have been proposed in this thesisnamely, (1) Context Switch Aware Large TLB (CSALT), an architecture which addresses the problem of increased TLB miss rates and their adverse impact on data caches. CSALT copes with the increased demand of context switches by storing a large number TLB entries. It mitigates data cache contention by

employing a novel TLB-aware cache partitioning scheme. On 8-core systems that switch between two virtual machine contexts executing multi-threaded workloads, CSALT achieves an average performance improvement of 85% over a baseline with conventional L1-L2 TLBs and 25% over a baseline which has a large L3 TLB (2) Translation Coherence using Addressable TLBs (TCAT), a hardware translation coherence scheme which eliminates almost all of the overheads associated with address translation coherence. TCAT overlays translation coherence atop cache coherence to accurately identify slave cores. It then leverages the addressable Part-Of-Memory TLB (POM-TLB) to eliminate expensive Inter Processor Interrupts (IPI) and achieve precise invalidations on the slave core. On 8-core systems with one virtual machine context executing multi-threaded workloads, TCAT achieves an average performance improvement of 13% over the kvmt1b baseline.

## Table of Contents

| Abstra     | act   |                                                                  | iv |

|------------|-------|------------------------------------------------------------------|----|

| List of    | Figu  | res                                                              | ix |

| Chapt      | er 1. | Introduction                                                     | 1  |

| 1.1        | Addre | ess Translation and Context Switching                            | 1  |

| 1.2        | Trans | slation Coherence                                                | 5  |

| Chapt      | er 2. | Virtual Memory in Virtualized Systems                            | 10 |

| 2.1        | Hard  | ware Virtualization                                              | 10 |

| 2.2        | Addre | ess Translation                                                  | 11 |

|            | 2.2.1 | Address Translation in Native Systems                            | 12 |

|            | 2.2.2 | Address Translation in Virtualized Systems                       | 12 |

| 2.3        | Trans | slation Coherence                                                | 14 |

|            | 2.3.1 | Translation Coherence in Native Systems                          | 15 |

|            | 2.3.2 | Translation Coherence in Virtualized Systems                     | 16 |

| Chapter 3. |       | Motivation: Virtual Memory Overheads in Virtualized Environments | 21 |

| 3.1        | Addre | ess Translation Overheads                                        | 21 |

| 3.2        | Virtu | al Memory Associated Overheads induced by Context Switch-        |    |

|            | ing . |                                                                  | 22 |

| 3.3        | Trans | slation Coherence Overheads                                      | 26 |

| Chapt      | er 4. | Related Work                                                     | 33 |

| 4.1        | Addre | ess Translation in Virtualized Environments                      | 33 |

|            | 4.1.1 | Translation Caching Structures                                   | 33 |

|            | 4.1.2 | Speculation Schemes                                              | 34 |

|            | 4.1.3 | Hiding Page Walk Latency and Increasing TLB reach .              | 34 |

|       | 4.1.4                                               | Translation-aware Cache Replacement and Cache Partitioning |  |  |

|-------|-----------------------------------------------------|------------------------------------------------------------|--|--|

| 4.2   | Trans                                               | lation Coherence                                           |  |  |

|       | 4.2.1                                               | Software Approaches                                        |  |  |

|       | 4.2.2                                               | UNITD: UNified Instruction/Translation/Data Coherence      |  |  |

|       | 4.2.3                                               | DiDi: A Shared TLB Directory                               |  |  |

|       | 4.2.4                                               | HATRIC: Hardware Translation Invalidation and Coherence    |  |  |

|       |                                                     |                                                            |  |  |

| Chapt | er 5.                                               | Architecture Description & Evaluation                      |  |  |

| 5.1   | Conte                                               | ext Switch Aware Large TLB                                 |  |  |

|       | 5.1.1                                               | CSALT with Dynamic Partitioning (CSALT-D)                  |  |  |

|       | 5.1.2                                               | CSALT with Criticality Weighted Partitioning (CSALT-CD)    |  |  |

|       | 5.1.3                                               |                                                            |  |  |

|       | 5.1.4                                               | Effect of Replacement Policy                               |  |  |

| 5.2   | Translation Coherence using Addressable TLBs (TCAT) |                                                            |  |  |

|       | 5.2.1                                               | Overview of our scheme                                     |  |  |

|       | 5.2.2                                               | Overlaying translation coherence atop cache coherence .    |  |  |

|       | 5.2.3                                               | Coherence lookups in the TLB                               |  |  |

|       | 5.2.4                                               | Achieving Translation Coherence                            |  |  |

|       |                                                     | 5.2.4.1 Initiator core operations                          |  |  |

|       |                                                     | 5.2.4.2 Slave core operations                              |  |  |

|       | 5.2.5                                               | Discussion                                                 |  |  |

|       |                                                     | 5.2.5.1 Why is Cache Line Flush required?                  |  |  |

|       |                                                     | 5.2.5.2 Assumptions                                        |  |  |

|       |                                                     | 5.2.5.3 Precision of Invalidation                          |  |  |

|       | 5.2.6                                               | Putting it all together                                    |  |  |

| Chapt | er 6.                                               | Results                                                    |  |  |

| 6.1   | Exper                                               | rimental Set-Up                                            |  |  |

| 6.2   | Conte                                               | ext-Switch Aware Large TLB                                 |  |  |

|       | 6.2.1                                               | Workloads                                                  |  |  |

|       | 622                                                 | Simulation                                                 |  |  |

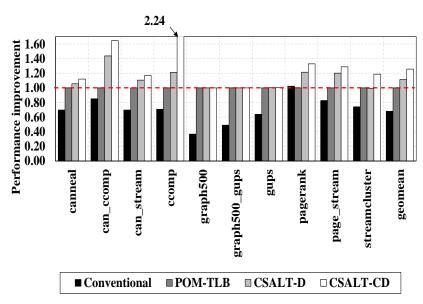

|         | 6.2.3  | CSALT Performance                              | 77 |

|---------|--------|------------------------------------------------|----|

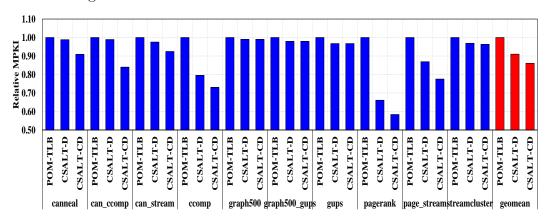

|         |        | 6.2.3.1 CSALT Performance in Native Systems    | 82 |

|         | 6.2.4  | Comparison to Prior Works                      | 82 |

|         | 6.2.5  | Sensitivity Studies                            | 85 |

| 6.3     | Trans  | lation Coherence using Addressable TLBs (TCAT) | 88 |

|         | 6.3.1  | Workloads                                      | 88 |

|         | 6.3.2  | Simulation                                     | 89 |

|         | 6.3.3  | TCAT performance                               | 90 |

|         | 6.3.4  | TCAT performance in Native Systems             | 92 |

| Chapte  | er 7.  | Conclusion                                     | 95 |

| Bibliog | graphy | <i>I</i>                                       | 97 |

## List of Figures

| 2.1 | Page table walk in Native Systems (1D-page walk)                                                                        | 13 |

|-----|-------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Page Table Walks in Virtualized Systems                                                                                 | 14 |

| 2.3 | TLB shootdowns in Native Systems                                                                                        | 17 |

| 2.4 | TLB shootdowns in Virtualized Systems                                                                                   | 20 |

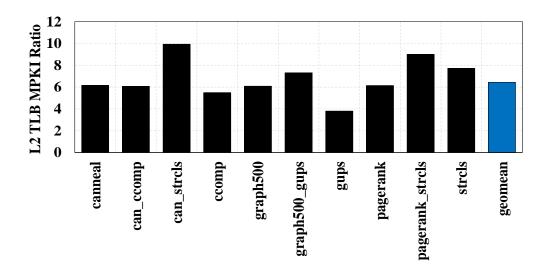

| 3.1 | Increase in TLB Misses due to Context Switches. Ratio of L2 TLB MPKIs in Context Switch Case to Non-Context Switch Case | 23 |

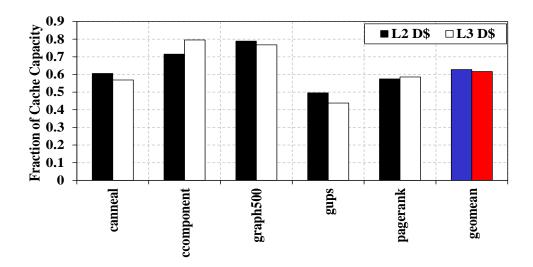

| 3.2 | Fraction of Cache Capacity Occupied by TLB Entries                                                                      | 25 |

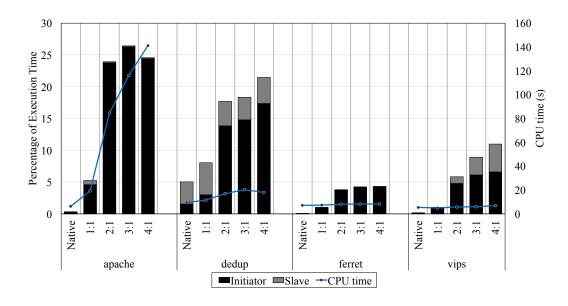

| 3.3 | Percentage Execution overhead of TLB shootdown (vCPU overcommit)                                                        | 31 |

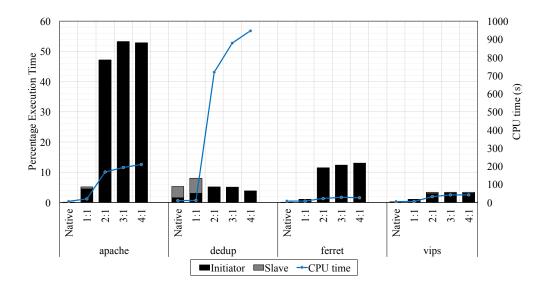

| 3.4 | Percentage Execution overhead of TLB shootdown (VM overcommit)                                                          | 31 |

| 3.5 | Average TLB Shootdown Latency                                                                                           | 32 |

| 5.1 | CSALT System Architecture                                                                                               | 42 |

| 5.2 | LRU Stack Example                                                                                                       | 49 |

| 5.3 | CSALT Overall Flowchart                                                                                                 | 50 |

| 5.4 | Coherence Scheme in action                                                                                              | 72 |

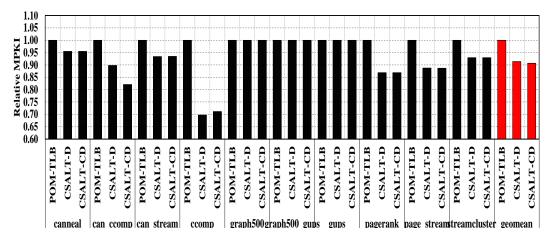

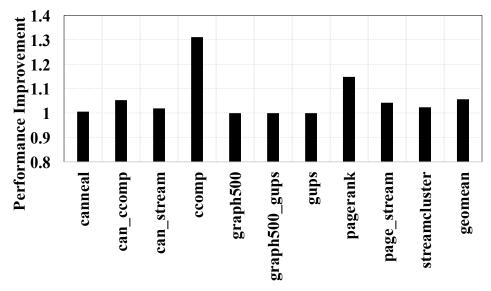

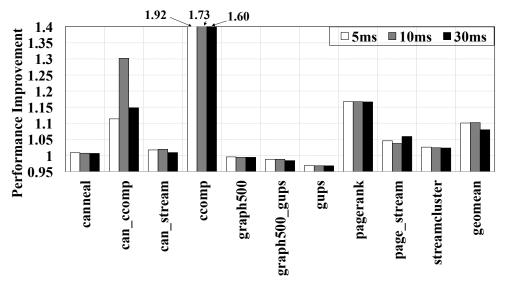

| 6.1 | Performance Improvement of CSALT (normalized to POM-TLB)                                                                | 77 |

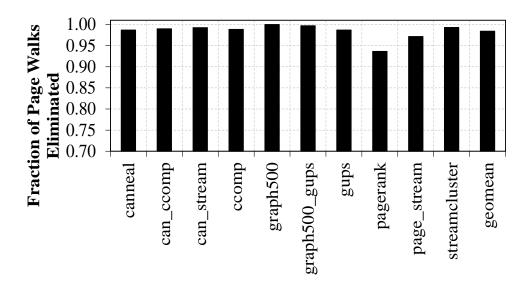

| 6.2 | POM-TLB: Fraction of Page Walks Eliminated                                                                              | 78 |

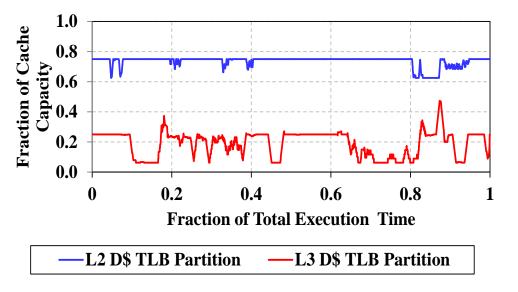

| 6.3 | Fraction of TLB Allocation in Data Caches                                                                               | 79 |

| 6.4 | Relative L2 Data Cache MPKI over POM-TLB                                                                                | 80 |

| 6.5 | Relative L3 Data Cache MPKI over POM-TLB                                                                                | 80 |

| 6.6 | Performance Improvement of CSALT-CD in the native context                                                               | 83 |

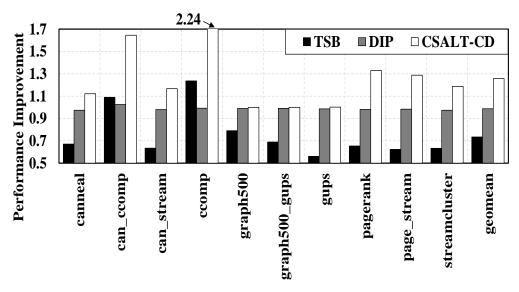

| 6.7 | Performance Comparison of CSALT with Other Comparable Schemes                                                           | 85 |

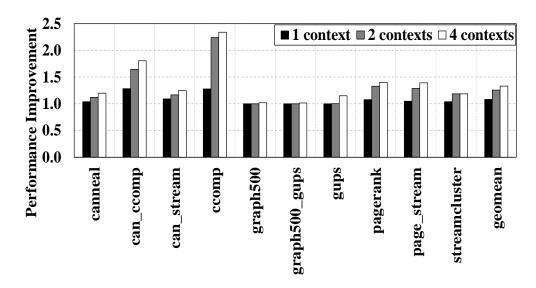

| 6.8 | Performance of CSALT with Different Number of Contexts                                                                  | 86 |

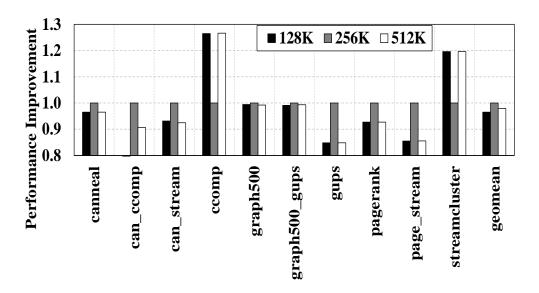

| 6.9 | Performance of CSALT with Different Epoch Lengths                                                                       | 87 |

| 0.5 | remained or Correr with Different Epoch Lengths                                                                         | 01 |

| 6.10 | Performance of CSALT with Different Context Switch Intervals | 87 |

|------|--------------------------------------------------------------|----|

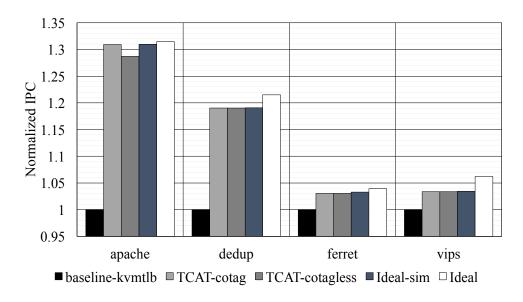

| 6.11 | Performance improvement of TCAT                              | 92 |

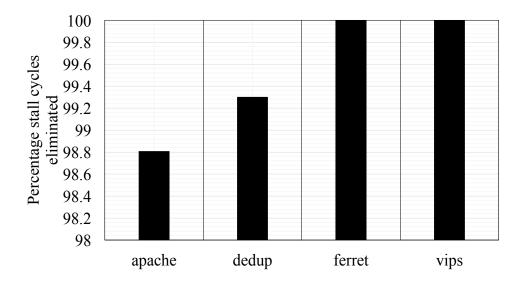

| 6.12 | Percentage stall cycles eliminated                           | 93 |

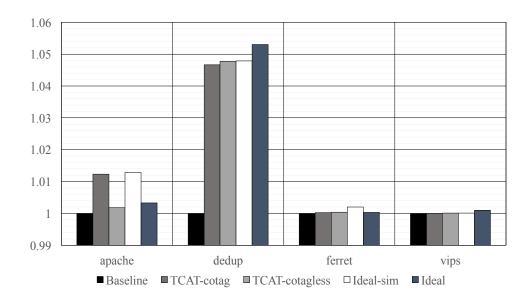

| 6.13 | Performance improvement in Native systems                    | 94 |

## Chapter 1

## Introduction

## 1.1 Address Translation and Context Switching

Computing in virtualized cloud environments [1–5] has become a common practice for many businesses in order to reduce capital expenditures. Many hosting companies have found that the utilization of their servers is low (see [6] for example). In order to keep the machine utilization high, the hosting companies that maintain the host hardware typically attempt to keep just enough machines to serve the computing load, and allowing multiple virtual machines to coexist on same physical hardware [7–9]. High CPU utilization has been observed in many virtualized workloads [10–12].

The aforementioned trend means that the host machines are constantly occupied by applications from different businesses, and frequently, different contexts are executed on the same machine. Although it is ideal for achieving high utilization, the performance of guest applications suffer from frequent context switching. The memory subsystem has to maintain consistency across the different contexts, and hence traditionally, processors used to flush caches and TLBs. However, modern processors adopt a more efficient approach where each entry contains Address Space Identifier (ASID)[13]. Tagging the entry

with ASID eliminates the needs to flush the TLB upon a context switch, and when the swapped-out context returns, some of its previously cached entries will be present. Although these optimizations worked well with traditional benchmarks where the working set, or memory footprint, was manageable between context switches, this trend no longer holds for emerging workloads. The memory footprint of emerging workloads is orders of magnitude larger than traditional workloads, and hence the capacity requirement of TLBs as well as data caches is much larger. This means the cache and TLB contents of previous context will frequently be evicted from the capacity constrained caches and TLBs since the applications need a larger amount of memory. Although there is some prior work that optimizes context switches [14–16], there is very little literature that is designed to handle the context switch scenarios caused by huge footprints of emerging workloads that flood data caches and TLBs.

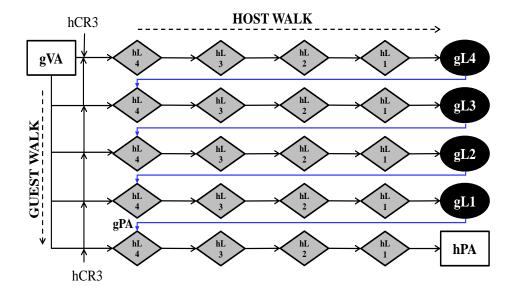

Orthogonally, the performance overhead of address translation in virtualized systems is considerable as many TLB misses incur a full 2-dimensional page walk. The page walk in virtualized system begins with guest virtual address (gVA) when an application makes a memory request. However, since the guest and host system keep their own page tables, the gVA has to be translated to host physical address (hPA). First, gVA has to be translated to guest physical address (gPA), which is the host virtual address (hVA). This hVA is finally translated to gPA. This involves walking down a 2-dimensional page table. Current x86-64 employs a 4-level page table[17], so the 2-dimensional

page walk may require up to 24 accesses. Making the situation worse, emerging architectures [18] introduce a 5-level page table resulting in the page walk operation to only get longer. Also, even though the L1-L2 TLBs are constantly getting bigger, they are not large enough to handle the huge footprint of emerging applications, and expensive page walks are becoming frequent.

Context switches in virtualized workloads are expensive. Since both the guest and host processes share the hardware TLBs, context switches across virtual machines can impact performance severely by evicting a large fraction of the TLB entries held by processes executing on any one virtual machine.

Conventional page walkers as well as addressable large-capacity translation caches (such as Oracle SPARC TSB [19]) generate accesses that get cached in the data caches. In fact, these translation schemes rely on successful caching of translation (or intermediate page walk) entries in order to reduce the cost of page walks. There has also been some recent work that attempts to improve the address translation problem by implementing a very large L3 TLB that is a part of the addressable memory[20]. The advantage of this scheme titled POM-TLB is that since the TLB is very large (several orders of magnitude larger than conventional on-chip TLBs), it has room to hold most required translations, and hence most page walks are eliminated. However, since the TLB request is serviced from the DRAM, the latency suffers. The POM-TLB entries are cached in fast data caches to reduce the latency problem, however, all of the aforementioned caching schemes suffer from the problem of cache contention due to the additional load on data caches caused

by the cached translation entries.

As L2 TLB miss rates go up, proportionately, the number of translation-related accesses also go up, resulting in congestion in the data caches. Since a large number of TLB entries are stored in data caches, now the data traffic hit rate is affected. When the cache congestion effects are added on top of cache thrashing due to context switching, which is common in modern virtualized systems, the amount of performance degradation is not negligible.

In this thesis, we present CSALT (read as "sea salt") which employs a novel dynamic cache partitioning scheme to reduce the contention in caches between data and TLB entries. CSALT employs a partitioning scheme based on monitoring of data and TLB stack distances and marginal utility principles. We architect CSALT over a large L3 TLB which can practically hold all the required TLB entries. However, CSALT can be easily architected atop any other translation scheme. CSALT addresses increased cache congestion when L3 TLB entries (or entries pertaining to translation in other translation schemes) are allowed to be cached into L2 and L3 data caches by means of a novel cache partitioning scheme that separates the TLB and data traffic. This mechanism helps to withstand the increased memory pressure from emerging large footprint workloads especially in the virtualized context switching scenarios.

#### 1.2 Translation Coherence

Beyond the problem of expensive address translations and TLB misses due to context switching, translation coherence has become a major performance sink in virtualized environments. Often, OSes perform modifications to the virtual-to-physical address translations to increase performance. For example, the OS may want to swap a page out to the disk or relocate a frequently used page to a faster memory. In either case, the OS must invalidate a virtual-to-physical address translation of the physical page being swapped out or relocated. To maintain a consistent view of virtual memory across cores, the OS must inform all the processors in a Chip Multi Processor (CMP) about this invalidation. Modern systems utilize Inter Processor Interrupts (IPIs) for this communication. The core which initiates the address translation modification, called the *initiator core*, relays IPIs to cores which might potentially hold the modified address translation in their private TLBs, called the *slave cores*. The initiator core then enters a busy wait loop waiting for acknowledgement from all the cores to ensure remote invalidation before proceeding further. Upon receiving the IPIs, the slave cores jump to an interrupt handler and perform invalidations in their own private TLBs. This process is called the TLB shootdown. There are several overheads involved in this process. First, processing the IPIs involve expensive pipeline flushes and protection level switches. Second, for the initiator core, remote invalidations pose a foreground overhead because of the busy-wait loop. In native systems, we observe that the initiator core spends thousands of CPU cycles waiting for acknowledgement from slave cores. In dedup benchmark from the PARSEC benchmark suite, we observe upto 8us of delay on a state-of-the-art Intel Skylake system. Third, the list of slave cores is approximated. The OS conservatively relays IPIs to cores which may potentially contain the modified translation. The slave may not contain the modified mapping due to reasons like TLB evictions[21][22].

In virtualized systems, TLB shootdowns occur between virtual processors (vCPUs) instead of the physical cores. The overall process of a TLB shootdown in virtualized environments looks very similar to native TLB shootdowns, albeit a few key differences. First, vCPUs generate virtual IPIs instead of physical IPIs. These virtual IPIs are emulated by the underlying Virtual Machine Manager (VMM), which performs the task of communicating to the slave vCPU that a translation has been modified, either by relaying a physical IPI to the physical core running the target vCPU, or by setting a flag to enforce coherence when target vCPU resume execution. TLB shootdowns in virtualized environments suffer from the same set of problems as their native counterparts: expensive pipeline flushes and protection level switches on the physical core upon delivery of the physical IPI, approximation of the list of slave vCPUs, and busy wait loop on the initiator vCPU. Interestingly, busy wait on the initiator vCPU is exacerbated because the slave vCPU might potentially get pre-empted while processing the virtual interrupt, delaying the acknowledgement [23]. In addition, due to imprecision of invalidation, the slave core must perform a TLB flush instead of an invalidation of a single translation entry. Therefore, we observe an order of magnitude increase in the busy wait to 60us on the initiator in dedup on Intel Skylake machine with 8 cores running a single VM with 8 vCPUs. Virtualized systems also suffer from the overhead of emulation of virtual interrupts.

TLB shootdowns in virtualized environments are woefully imprecise, imposing additionally overheads on an already worse baseline. Current VMMs do not track the guest virtual address. Since modern processors only permit invalidations of individual TLB entries when the gVA is known, when the VMM updates the nested page table, translation structures are completely flushed [24]. Additionally, VMMs track address translations at VM-granularity - VMMs track the subset of cores that a vCPU runs on, but do not track the subset of cores that a process on a vCPU runs on. To make matters worse, even the initiator vCPU can only approximate the list of slave vCPUs which have potentially accessed the translation being modified. As a result, in addition to the list of slave vCPUs approximated by the guest OS, the list of slave cores is approximated by the VMM. Combined with the flushing of translation structures upon a nested page table update, these approximations result in translations pertaining to other processes that run on the target vCPU being needlessly invalidated [24].

There have been various techniques proposed in both hardware and software to eliminate these overheads. Software schemes like Lazy Translation Coherence [25], ABIS[26] and hardware schemes like DIDI[21], UNITD[22] and HATRIC [24] aim to reduce the number of IPIs or eliminate them altogether. Hardware schemes allow precise identification of the slave cores and eliminate

busy waits on the initiator. However, some of these schemes are applicable only to native environments. While HATRIC[24] does account for virtualized environments, it suffers from two major drawbacks. First, HATRIC tags the TLB entries with the physical address of the last-level PTE of the host page table. As a result, it can only track changes to the host page table, and cannot track changes to the guest page table. Also, since the TLB entries are tagged with the physical address of the last-level PTE, it cannot track changes to the intermediate host PTEs. Second, HATRIC does not solve the problem of imprecision in virtualized environments. Even with HATRIC, when the VMM updates the nested page table, translation structures are completely flushed.

In this thesis, we present TCAT (Translation Coherence using Addressable TLBs), a hardware translation coherence scheme to reduce the cost of address translation coherence. TCAT overlays translation coherence atop cache coherence. It then leverages the addressable Part of Memory TLB (POM-TLB) [27] to enable precise invalidations in virtualized environments. TCAT tracks changes to guest page table by tying each guest page table translation to a single address in POM-TLB. On a guest-page table updates, TCAT generates coherence messages for that POM-TLB address. When the other cores see these coherence messages, they know which entry in their TLB needs to be invalidated, because each guest page table translation is tied to a single address in the POM-TLB. This allows precise invalidations on the slave vCPUs/cores. This mechanism helps withstand the overheads of page-table modifications by the guest OS.

This thesis is structured as follows. Chapter 2 provides a brief background on address translation and translation coherence in both native and virtualized environments. In Chapter 3, we motivate the need for our solutions by demonstrating the overheads that exist in virtual memory in current virtualized systems. In Chapter 4, we explore the existing solutions and their drawbacks. In Chapter 5 and 6, we present our design and evaluate the results. Chapter 7 concludes the thesis.

## Chapter 2

## Virtual Memory in Virtualized Systems

#### 2.1 Hardware Virtualization

Hardware virtualization is an abstraction of computing resources from the software that uses those resources. In a traditional computing environment, the operating system or an application has direct access to the underlying computing resources such as the processor, memory and storage. In order to facilitate server consolidation, hardware virtualization installs a hypervisor or virtual machine manager (VMM), which creates an abstraction layer between the software and the underlying computing resources. In the presence of a hypervisor, software uses the virtual representations of underlying computing resources such as virtual processors (vCPUs) or guest memory instead of using those resources directly. Virtualized computing resources are provisioned into isolated independent instances called virtual machines (VMs) where operating systems and applications can be installed. The operating system running on the VM along with its associated software is termed the guest, and the underlying hardware which provides the computing resources for the guest to run is termed the host. Virtualized systems can host multiple VMs simultaneously, but every VM is logically isolated from every other VM.

#### 2.2 Address Translation

All modern computer systems provide an abstraction of main memory known as Virtual Memory. This abstraction ensures efficient use of main memory, provides an uniform address space to all processes, and achieves memory isolation between processes. In a system with virtual memory support, while each byte on the main memory is addressable by a unique address called the Physical Address (PA), a processor which intends to perform a memory access generates a Virtual Address (VA). Before accessing memory, VA is converted to PA in a process known as Address Translation. This process is performed at the granularity of a fixed-size block, rather than the granularity of a single virtual address. Virtual memory is partitioned into fixed-size blocks of  $P=2^p$ bytes called Virtual Pages. Main memory, addressed by PA, is partitioned into fixed-size blocks of the same size  $(P = 2^p \text{ bytes})$  called Page Frames or Physical Pages. Address translation maps a virtual page to a physical page, and is achieved by means of a data structure stored in physical memory called the Page Table that stores mappings of virtual pages to physical pages. A page table is organized as an array of page table entries (PTEs). A PTE comprises of the VA-PA mapping, a valid bit indicating if the mapping is valid or not, and metadata associated with the mapping. Metadata fields vary widely across architectures. Each page in the virtual address space has a PTE at a fixed offset in the page table. Therefore, given a VA, the address translation hardware can index into the page table with an appropriate offset and obtain the PA from the PTE. To reduce the memory requirements of a page table, multi-level page tables are used in modern systems. In case of today's x86-64, a four-level page table is adopted. To obtain the VA-PA mapping, the address translation hardware has to access all page table levels in a process called the page table walk. Since address translation needs to be performed on every memory access, it is critical to processor performance. Therefore, all processors employ a Translation Lookaside Buffer (TLB), which caches VA-PA mappings in an on-chip, content-addressable memory and eliminates the need for a full page table walk in the common case.

#### 2.2.1 Address Translation in Native Systems

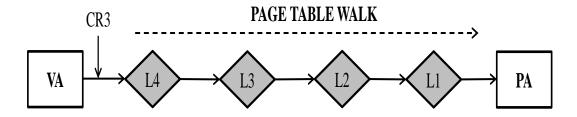

The procedure to perform the full translation in a native setting as is shown in Figure 2.1. The first few most significant bits (MSBs) of the VA are used along with the CR3 register to index into the first level of the page table, which is denoted as L4 in the figure. The entry at that index in L4 points to the base of L3. The next few MSBs of the VA are used to index into L3, and the entry at that index points to the base of L2. This process is continued until the last level L1 yields the PA corresponding to the VA. Therefore, in order to obtain a full translation, upto 4 memory accesses have to performed with a four-level page table.

#### 2.2.2 Address Translation in Virtualized Systems

With hardware virtualization, to fully virtualize memory, two levels of address translation are used: (1) guest virtual address (gVA) to guest physical

Figure 2.1: Page table walk in Native Systems (1D-page walk)

address translation (gPA) via a per-process guest OS page table (gPT) (2) guest physical address (gPA) to host physical address (hPA) via a per-VM host page table (hPT). Address translation in modern systems with hardware virtualization support is usually performed by a hardware technique called Nested Paging. The processor has two page table pointers to perform the two levels of address translation: one points to the guest page table (gCR3) and the other points to the host page table (hCR3). The guest page table holds gVA to gPA translation and the host page table holds gPA to hPA translations. In the best case, the gVA to hPA translation is available in the TLB. In the worst case, a TLB miss necessitates a 2D page walk. In a 2D page walk, a guest page table walk proceeds in the same way a native page table walk does. However, since guest memory is virtual, each guest page table access necessitates a host page table walk (which again proceeds in the same way as a native page table walk) to obtain the hPA. Once the hPA is obtained, the guest page table is accessed on the host physical memory, and the pointer to the next level of the guest page table is obtained. Page table memory references grow from a native 4 to a virtualized 24 references: 4 accesses to translate gCR3 (since each gPA requires access to host page table) and each of the 4 levels of the guest page

Figure 2.2: Page Table Walks in Virtualized Systems

table (guest page table holds gPA) plus 4 accesses for the guest page table itself; to obtain the final hPA:  $4 \times 5 + 4 = 24$  references.

## 2.3 Translation Coherence

As TLBs are critical to processor performance, each core in a chip multiprocessor (CMP) has its own private TLB. Additionally, depending on the architecture, each core might contain private translation structures such as MMU caches and Nested TLBs (nTLB) to mitigate the overheads of full page walk in the common case. This replication mandates that all translation structures must be kept consistent with the OS page tables, so that the information cached in each one of these structures preserves a globally consistent view of virtual memory. There are a number of scenarios in which

the information associated with a translation may change: free operations like munmap() and madvise(); migration operations like page swap, deduplication and compaction; permission change operations like mprotect(); ownership change operations like copy-on-write optimization; and remap operations like mremap(). The aforementioned operations either update the mapping itself, or update the metadata bits associated with the mapping. During such events, consistency has to be maintained across private TLBs for correctness - no core should access a stale translation. Translation coherence is a way to enforce this consistency. In modern systems, TLBs are kept coherent at the software-level by the operating system (OS). Whenever the OS modifies a translation, it must initiate a coherency transaction among TLBs, a process known as a TLB shootdown. Current CMPs rely on the OS to approximate the set of TLBs caching a mapping and synchronize TLBs using costly Inter-Processor Interrupts (IPIs) and software handlers.

#### 2.3.1 Translation Coherence in Native Systems

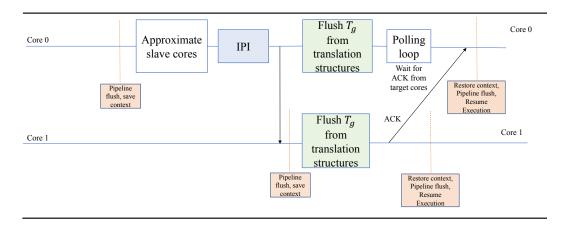

A TLB shootdown is an elaborate transaction in which the core initiating a modification the page-table ensures that all cores invalidate the affected mapping from their TLBs. The time line of a TLB shootdown in native environments is as illustrated below. Figure 2.3 depicts the sequence of events in a native system when a TLB shootdown is triggered to invalidate a mapping  $T_q[21][22]$ .

1. One of the physical cores executing an operation that modifies the page-

table, referred to as the initiator core, prompts the OS to lock the corresponding page table entry and disables kernel pre-emption.

- 2. The OS forms a list of physical cores, called the slave cores or target cores, that requested a translation of the modified page-table entry in the past. The list of slave cores is conservatively approximated, since all cores in the list might not contain the modified translation due to TLB evictions.

- 3. The initiator sends an IPI to all the slave cores, requesting them to invalidate the TLB entries referring to the modified mapping. Meanwhile, the initiator core invalidates the mapping in its private TLB and waits for acknowledgments from all the slave cores.

- 4. All slave cores receive the IPI and execute the IPI handler for TLB invalidations. The interrupt handler code invalidates any affected TLB entries and sends an acknowledgement to the initiator core.

- 5. Once all acknowledgements are received by the initiator core, the OS unlocks the modified page-table entry, enables kernel pre-emption and continues its execution.

#### 2.3.2 Translation Coherence in Virtualized Systems

With hardware virtualization, there is an abstraction layer sitting atop the underlying hardware - as a result, the guest processes execute on virtual

Figure 2.3: TLB shootdowns in Native Systems

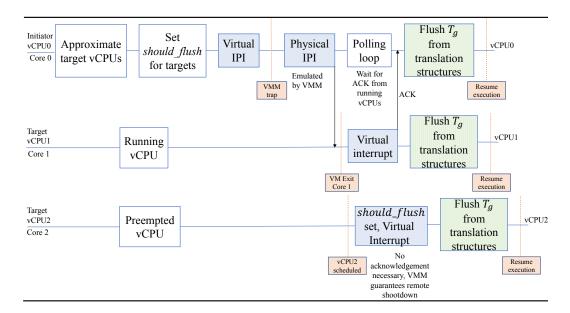

processors (vCPUs) and not directly on the physical cores. TLB shootdown in virtualized environments must therefore ensure that all vCPUs invalidate the affected mapping from their virtual TLBs. The time line of a TLB shootdown in virtualized environments is as illustrated below. Figure 2.4 depicts the sequence of events in a virtualized system when a TLB shootdown is triggered to invalidate a mapping  $T_g[24][23]$ .

- 1. One of the vCPUs executing a page-table modification operation, referred to as the initiator vCPU, prompts the guest OS to lock the corresponding page table entry.

- 2. The guest OS approximates a list of vCPUS, called the target vCPUs, that requested a translation of the modified page-table entry in the past.

- 3. The initiator vCPU sends an IPI with a specific vector number to a set of target vCPUs. The initiator then enters a polling based loop until all

target vCPUs have processed and acknowledged the requests by setting a flag located in shared memory.

- 4. The IPI transmission by the vCPU causes the hardware to trap into the VMM. The VM emulates the IPI and generates a new IPI that is transmitted to the VMM on the physical cores hosting the target vCPUs.

- 5. When the IPI is delivered to the physical core hosting the target vCPU, it causes a VM trap. The IPI is handed off the VMM running on the physical core. The VMM then injects a virtual interrupt to the target vCPU.

- 6. As soon as the target vCPU resumes execution, it executes the IPI handler for TLB invalidations. The interrupt handler code invalidates any affected TLB entries and sends an acknowledgement to the initiator vCPU by setting a flag located in shared memory.

- 7. Once all acknowledgements are received by the initiator vCPU, the guest OS unlocks the modified page-table entry and resumes normal execution.

In native environments, TLB shootdowns are comparatively faster. This is because the initiator physical core has to wait for target physical cores to acknowledge before the IPI is handled -and the target physical core is always available. However, in virtualized environments, since vCPUs are merely processes running on the host, a target vCPU could potentially be preempted by the host scheduler. In other words, target vCPUS are not always available to

send the acknowledgement to the initiator vCPU. Target vCPUs can perform the invalidation and send the acknowledgement only when they are scheduled again. This can result in the latencies of TLB flush operations increasing by orders of magnitude depending on the scheduling state of the target vCPUs. This problem is referred to as the TLB shootdown preemption problem[23]. In order to circumvent this problem, KVM utilizes a scheme called KVM paravirtual remote flush TLB scheme (kvmtlb) developed by the Linux community. This scheme records the preemption state of all vCPUs inside the VMM and shares this information with the VM. When there is a nested page table update, if the target vCPU is running, TLB shootdown proceeds like in the native case. However, if the target vCPU is preempted, a should\_flush flag is set on that target vCPU and the IPI is not sent. When rescheduling a vCPU, the VMM checks the should\_flush flag. If set, the VMM invalidates all TLB entries of that vCPU. This eliminates the problem of increased latencies on the initiator vCPUs waiting for acknowledgements from the remote vCPU[23].

Figure 2.4: TLB shootdowns in Virtualized Systems

## Chapter 3

## Motivation: Virtual Memory Overheads in Virtualized Environments

#### 3.1 Address Translation Overheads

In native systems, address translation overhead is considerable as a result of multiple memory references (proportional to the depth of the page table) required to obtain a full translation. Although techniques like caching of page table entries in data caches, MMU caches and caching intermediate translations can remove some of the memory references for a TLB miss, address translation in native systems still incurs a non-negligible performance overhead. In virtualized systems, the address translation overhead increases as a result of the increased number of memory references required to obtain a full translation due to a 2D page table walk. Table 3.1 lists the measured page walk cost per L2 TLB miss in both native and virtualized systems for some PARSEC and graph workloads. Measurements were made on a state-of-the-art Intel Skylake system with extended page tables. While some workloads (e.g., streamcluster) have very similar page walk costs in both native and virtualized, others (e.g., connected component, gups) show significant increase under virtualization as expected. With the increase in the number of page table levels, these overheads will only be exacerbated.

| Benchmark          | Native | Virtualized |

|--------------------|--------|-------------|

| canneal            | 53     | 61          |

| connectedcomponent | 44     | 1158        |

| graph500           | 79     | 80          |

| gups               | 43     | 70          |

| pagerank           | 51     | 61          |

| streamcluster      | 74     | 76          |

Table 3.1: Average Page Walk Cycles Per L2 TLB miss

# 3.2 Virtual Memory Associated Overheads induced by Context Switching

Today, it is common to have multiple VM instances to share a common host system as cloud vendors try to maximize hardware utilization. The aforementioned trend means that the host machines are constantly occupied by applications from different businesses, and frequently, different contexts are executed on the same machine. Although it is ideal for achieving high utilization, the performance of guest applications suffer from frequent context switching.

Context switches in virtualized workloads are expensive. Since both the guest and host processes share the hardware TLBs, context switches across virtual machines can impact performance severely by evicting a large fraction of the TLB entries held by processes executing on any one virtual machine. To quantify this, we measured the increase in the L2 TLB MPKI of a context-switched system (2 virtual machine contexts, switched every 10ms) over a non-context-switched baseline. Figure 3.1 illustrates the increase in L2 TLB MPKIs for several multi-threaded workloads, when additional virtual machine context

Figure 3.1: Increase in TLB Misses due to Context Switches. Ratio of L2 TLB MPKIs in Context Switch Case to Non-Context Switch Case

switches are considered. Despite only two VM contexts, the impact on the the L2 TLB is severe: an average increase in TLB MPKI of over 6X. This leads to an overall degradation in performance of the context-switched workloads. For instance, when 1 VM instance of pagerank was context-switched with another VM instance of the same workload, the total program execution cycles for each instance went up by a factor of 2.2X.

The higher miss rate of the L2 TLB leads to increased translation traffic to the data caches. In the conventional radix tree based page table organization, the additional page walks result in the caching of intermediate page tables. In the POM-TLB organization, the caches store translation entries instead of page table entries. By translation entry we refer to a TLB entry that stores the translation of a virtual address to its physical address. While

caching of TLB entries inherently causes less congestion (one entry per translation as opposed to multiple intermediate page table entries), it still results in polluting the data caches when the L2 TLB miss rates are high. This scenario creates an undesirable situation where neither data nor TLB traffic achieves the optimal hit rate in data caches. A conventional system is not designed to handle such scenarios as the conventional cache replacement policy does not distinguish different types of cache contents. This is no longer true as some contents are data contents while others are TLB contents. When a replacement decision is made, it does not distinguish TLB contents versus data contents. But the data and TLB contents impact system performance differently. For example, data requests are overlapped with other data requests with the help of MSHR. On the other hand, an address translation request is a blocking access, so it stalls the pipeline. Although newer processor architectures such as Skylake have simultaneous page table walkers to allow up to two page table walks, the page table walk being a blocking access does not change. In the end, the conventional content-oblivious cache replacement policy makes both the TLB and data access performance suffer by making them compete for entries in capacity constrained data caches. This problem is exacerbated when frequent context switches occur between virtual machines.

To quantify the cache congestion problem, we measure the *occupancy* of TLB entries in L2 and L3 data caches. We define *occupancy* as the average fraction of cache blocks that hold TLB entries. To collect this data, we modified our simulator to maintain a type field (TLB or data) with each cache

Figure 3.2: Fraction of Cache Capacity Occupied by TLB Entries

block; periodically the simulator scanned the caches to record the fraction of TLB entries held in them. Figure 3.2 plots this data for several workloads. We observe that an average of 60% of the cache capacity holds translation entries. In one workload (connected component), the TLB entry occupancy is as high as 80%. This is because the L2 TLB miss rate is approximately 10 times the L1 data cache miss rate, as a result of which translation entries end up dominating the cache capacity.

In summary, context switching increases L2 TLB MPKI, which in turn causes increased translation traffic and congestion in the data caches. While caching of the translation entries is useful to avoid DRAM accesses, the above data suggests that unregulated caching of translation entries has a flip side of causing cache pollution or creating capacity conflict with data entries. If the congestion favors TLB contents while data contents are of more importance,

performance will suffer. On the other hand, if the congestion favors data contents while TLB contents are of more importance, performance will still suffer. However, in the latter case, in virtualized environments, an expensive 2D page walk has to be performed to obtain a gVA to hPA translation, which further worsens the performance impact of such a scenario.

#### 3.3 Translation Coherence Overheads

TLB shootdowns are employed in modern CMPs to maintain a globally consistent view of virtual memory. As discussed in Section 2.3.2, TLB shootdowns utilize costly IPIs and protection level switches to maintain coherence. As a result, they impose a considerable execution overhead. In native systems, these overheads can be broken up into three distinct components [21] in the following manner: (1) IPI delivery overhead: Overhead incurred by the initiator core in approximating the set of slave cores and delivering IPIs to each one of them (2) TLB invalidation overhead: Overhead of executing the handler which performs TLB invalidation on the initiator core (local shootdown), and TLB invalidation on the slave core (remote shootdown). This overhead is incurred by both the initiator core and the slave core (3) Busy wait overhead: Overhead of busy wait for acknowledgements from all the slave cores indicating that they have flushed the modified mapping from their TLBs. Only the initiator core sees this overhead.

TLB shootdowns in virtualized systems incur a few additional overheads. Since vCPUs are processes running on the host, IPIs delivered by the initiator vCPUs must be transmitted to the physical cores running the target vCPUs. Additionally, the physical core running the target vCPU must guarantee a remote TLB invalidation. This is enabled by the emulation of virtual interrupts by the VMM, which involves the penalty of conversion of virtual IPI into physical IPI and back into virtual IPI, and the penalty of a VM-exit on the slave physical core. In addition to these undesirable overheads, there are several inefficiencies associated with TLB shootdown in virtualized systems, as summarized below.

- 1. Imprecise invalidations: In a virtualized system, when the VMM updates the nested page table, it only tracks the gPA and the hPA. It does not track the gVA. Modern processors do not permit precise invalidations if the gVA is not known. This results in a complete flush of all translation structures on the cores containing the modified mapping. Repopulating these flushed structures incur the penalty of a 2D-page table walk[24].

- 2. Expensive remote TLB invalidations: TLB invalidations on the slave core/vCPU involve expensive pipeline flushes and protection level switch to execute privileged instructions. This interferes with the workloads executing on the slave cores[21].

- 3. Slave cores/vCPUs are approximated: In a native system, the list of slave cores is approximated. Therefore, some cores which may not possess the modified mapping needlessly flush their pipeline and execute

the interrupt handler upon IPI delivery. In a virtualized system, VMMs track the subset of cores that a vCPU runs on, and do not track the subset of cores that a process on a vCPU runs on. In other words, mappings are tracked at the VM-granularity rather than a process-within-a-VM granularity. Therefore, when the VMM remaps a page pertaining to a process running on the initiator vCPU, it conservatively issues IPIs to all physical cores that may potentially have executed any target vCPU. As in the native case, if the target physical core (which has potentially run the target vCPU in the past) does not have the modified mapping, it incurs the overhead of pipeline flush and interrupt handler execution. Additionally, translation entries pertaining to other processes that run on the target vCPU get needlessly invalidated due to flushing of the translation structures[24].

To summarize these overheads in a succinct manner, in our measurements, we have broken up TLB shootdown overheads into two distinct components: (1) Initiator core (native) or Initiator vCPU (virtualized) overheads (2) Slave core (native) or Target vCPU (virtualized) overheads. Initiator overheads are comprised of the IPI delivery overhead, TLB invalidation overhead, and the busy wait overhead. Slave/Target overheads are solely constituted by remote TLB invalidation overheads. We measure these components independently on a real system. We compute the total execution overhead of TLB shootdowns as the summation of all the initiator overheads and all the slave overheads.

We perform the measurements a 8-core state-of-the-art Intel Skylake

system with and without hardware virtualization. To collect this data, we use the Linux perf utility in conjunction with the Linux ftrace utility. perf utility provides precise information about the local and remote shootdown events, while ftrace utility is used to measure latencies of these individual events.

While performing measurements, we demonstrate the behavior with two different modes of oversubscription: (1) A single VM with a vCPU: CPU ratio of 1:1, 2:1 3:1 and 4:1. In this mode, oversubscription is due to running multiple vCPUs. (2) Multiple VMs, each with a vCPU: CPU ratio of 1:1. In this mode, oversubscription is due to the presence of multiple VMs. In this mode, a single VM runs the benchmark of interest, while all the other VMs run a CPU-intensive benchmark from sysbench[28][23]. Both these modes are commonly used in datacenters: the first mode is used typically used to boost CPU utilization, while the second mode is used to run multiple services at once. Typically, the ratio of the number of virtual CPUs (vCPUs) in the virtualized system to the number of physical cores present on the host is called the overcommit ratio. Overcommit ratios ranging from 2:1 to 6:1 are commonplace for the maximizing CPU utilization[4].

Figure 3.3 plots the percentage of execution time spent in TLB shoot-downs with the first mode of oversubscription for four workloads: apache, dedup, ferret and vips. For comparison, we plot the percentages for native environment, and virtualized environments with overcommit ratios of 1:1, 2:1, 3:1 and 4:1. We observe that the time spent doing TLB shootdowns typically increases with overcommit and can consume a considerable portion of

the application runtime across benchmarks. The proportion of time spent in the initiator and slave cores varies widely across benchmarks, although the overheads on the initiator usually larger. In *apache*, time spent in the initiator doing TLB shootdowns constitutes around 25% the execution for higher overcommit ratios. This can be attributed to wasteful busy waits on the initiator. In *vips*, the proportion of time spent on the slave increases with overcommit. This can be attributed to the imprecision of invalidation in virtualized environments.

Figure 3.4 plots the percentage of execution time spent in TLB shoot-downs with the second mode of oversubscription. In *apache*, the percentage overhead increases from 25% in the previous mode to 50%. Although *vips* and *dedup* spend more time doing TLB shootdowns, the percentage overhead decreases due to the large increase in the execution time. However, in *ferret*, percentage overhead increases and reaches upto 15% in the 4:1 overcommit case.

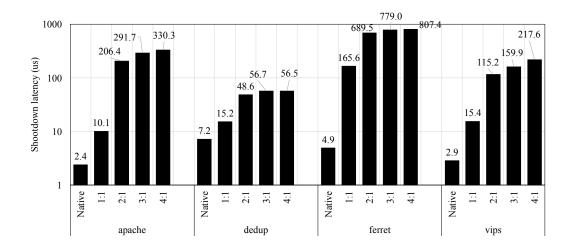

Figure 3.5 plots the average TLB shootdown latency with different overcommit ratios with the first mode of oversubscription. We consistenty observe higher average TLB shootdown latencies in virtualized environments. In most of the benchmarks, there is a noticeable jump in the shootdown latency from the 1:1 overcommit case to the 2:1 overcommit case. In *apache*, the latency increases 20X from the 1:1 to 2:1 overcommit case. In *vips*, we observe a 10-fold increase in latency from the 1:1 to 2:1 overcommit case. From 10us in the native case, average TLB shootdown latencies exhibit an order of magni-

Figure 3.3: Percentage Execution overhead of TLB shootdown (vCPU overcommit)

Figure 3.4: Percentage Execution overhead of TLB shootdown (VM overcommit)

Figure 3.5: Average TLB Shootdown Latency

tude increase to 100-1000us in virtualized environments with oversubscription. These behaviors can be attributed to the additional overheads associated with virtualization. We see that reducing the TLB shootdown costs would result in a considerable performance boost. This motivates us to design a translation coherence scheme which amortizes the overheads associated with TLB shootdowns in virtualized environments - like the busy wait on the initiator and imprecise invalidations on the slave.

## Chapter 4

## Related Work

## 4.1 Address Translation in Virtualized Environments

## 4.1.1 Translation Caching Structures

Oracle UltraSPARC mitigates expensive software page walks by using TSB [19]. Upon TLB misses, the trap handling code quickly loads the TLB from TSB where the entry can reside anywhere from the L2 cache to off-chip DRAM. However, TSB requires multiple memory accesses to load the TLB entry in virtualized environments as opposed to a single access in our scheme (refer to Figure 15 in [29] for an overview of the TSB address translation steps in virtualized environments). Further, our TLB-aware cache partitioning scheme is applicable to the TSB as well, and as demonstrated in Section 6.2.2, TSB architecture also sees performance improvement.

Modern processors implement MMU caches such as Intel's PSC [17] and AMD's PWC [30] that store partial translation to eliminate page walks. However, the capacity is still much smaller than application footprints that a large number of page walks are still inevitable. Other proposals like cooperative caching [31], shared last level TLBs [32], and cooperative TLBs [33] exploit predictable memory access patterns across cores. These techniques are orthogonal to our approach and can be applied on top of our scheme since

we use a shared TLB implemented in DRAM. Although software-managed TLBs have been proposed for virtualized contexts [34], we limit our work on hardware managed TLBs.

#### 4.1.2 Speculation Schemes

Speculation schemes [35,36] continue the processor execution with speculated page table entries and invalidate speculated instructions upon detecting the mispeculation. These schemes can effectively hide the overheads of page table walks. On the other hand, our scheme addresses the problem of TLB capacity. We aim to reduce the number of page walks significantly by having much larger capacity.

## 4.1.3 Hiding Page Walk Latency and Increasing TLB reach

Huge pages (e.g., 2MB or 1GB in x86-64) can reduce TLB misses by having a much larger TLB reach [37–39]. Our approach is orthogonal to huge pages since our TLB supports caching TLB entries for multiple page sizes. Various prefetching mechanisms [33, 40] have been explored to fetch multiple TLB or PTE entries to hide page walk miss latency. However, the fundamental problem that the TLB capacity is insufficient is not addressed in prior work. Hybrid TLB coalescing[41] aims to increase TLB coverage by encoding memory contiguity information and does not deal with managing cache capacity. Page Table Walk Aware Cache Management [42] uses a cache replacement policy to preferentially store page table entries on caches and does not use cache

partitioning.

# 4.1.4 Translation-aware Cache Replacement and Cache Partitioning

Recent cache replacement policy work such as DIP [43], DRRIP [44], SHiP [45] focuses on homogeneous data types, which means they are not designed to achieve the optimal performance when different data types of data (e.g., POM-TLB and data entries) coexist. Hawkeye cache replacement policy [46], also targets homogeneous data types, has a considerable hardware budget for LLC, and cannot be implemented for L2 data caches. EVA cache replacement policy [47] cannot be used in this case due to a similar problem.

Cache partitioning is an extensively researched area. Several previous works ([48–62]) have proposed mechanisms and algorithms for partitioning shared caches with diverse goals of latency improvement, bandwidth reduction, energy saving, ensuring fairness and so on. However, none of these works take into account the adverse impact of higher TLB miss rates due to virtualization and context switches. As a result, they fail to take advantage of this knowledge to effectively address the TLB induced cache congestion.

## 4.2 Translation Coherence

We have shown that translation coherence, which is currently an expensive operation implemented in software on most systems, can consume 10 to 30 percent of the application runtime. This observation is corraborated by various studies which show similar results[63]. These overheads mainly arise due to various inefficiencies of TLB shootdowns. In native environments, inefficiencies arise due to long latencies between with IPI delivery and reception of acknowledgement from the target cores, and inaccurate approximations of the slave cores causing unnecessary pipeline flushes. In virtualized environments, the latency problem is worsened due to TLB shootdown pre-emption. Additionally, precise invalidation of TLB entries is not possible in virtualized environments because hypervisors only track the guest physical and host physical page numbers. In order to eliminate these inefficiencies, various techniques have been proposed in both software and hardware.

## 4.2.1 Software Approaches

Oskin et al [64] propose a scheme for hardware-assisted TLB shoot-down. Hardware-assisted TLB shootdown approach introduces a special form of IPI, called the *REMOTE\_INVLPG*, and an associated microcode change that receives this special IPI and issues a TLB shoot-down process entirely in microcode without necessitating any OS interaction. This approach eliminates OS interaction on the slave cores. However, this approach still necessitates the initiator core to deliver IPIs and wait for acknowledgements from all the slave cores, therefore, it incurs the entire initiator overhead component elaborated in the previous section.

Amit et al [26] introduce Access Based Invalidation System (ABIS). They assert that that access bits of the PTE can be used to determine if the PTE is cached in any of the several private TLBs on the CMP. They use this information to avoid sending IPIs upon updates to mappings that are private, thereby preventing some of the penalties associated with both the initiator and the slave. However, ABIS requires extensive hardware support for direct TLB insertion and complex software infrastructure like a secondary page-hierarchy.

Mohan et al [25] propose a software-based TLB shootdown mechanism called Lazy-Translation Coherence that can alleviate the overhead of the TLB shootdown mechanism by handling TLB coherence in a lazy manner for page-table update operations that do not enforce synchronous updates. Lazy Translation Coherence avoids expensive IPIs which are required for delivering a shootdown signal to remote cores and the performance overhead of associated interrupt handlers. However, Lazy-translation coherence is only applicable for operations that can update the TLB asynchronously and cannot be applied for operations that enforce synchronous translation updates like *mprotect* or *mremap*.

Ouyang et al [23] propose a paravirtual TLB shootdown scheme named Shoot4U, which eliminates TLB shootdown preemptions in virtualized environments. It does so by intercepting remote vCPU TLB flush operations and performing the invalidations directly in the VMM instead of handling them in the guest environment. This optimization allows Shoot4U to avoid any delays caused by a vCPU which has been pre-empted and to ensure that the delays are consistent. Although Shoot4U decouples TLB shootdown completion from the host scheduler behaviors, it does not eliminate the busy wait loop on the

physical core on which the initiator vCPU is running. Additionally, it does not eliminate expensive IPIs between the physical cores.

## 4.2.2 UNITD: UNified Instruction/Translation/Data Coherence

Romanescu et al [22] propose a scalable hardware-based TLB coherence protocol called UNITD. The idea behind UNITD is to identify whether or not a page translation is present in a specific TLB by augmenting each TLB entry with the physical address of the last-level PTE of the translation that it holds. This is done by using structure called the Page Table Entry CAM (PCAM). Whenever the OS changes a PTE, the change propagates to the last-level PTE, and the cache-coherence protocols detect and relay this information to all the translation structures. Lookups are performed in the PCAM using the physical address of this last-level PTE, and TLB entries which are tagged with the same physical address are invalidated. There are two major drawbacks to this scheme: (1) It cannot track changes to intermediate PTEs. Although the authors argue that all the changes to the intermediate PTE need to be propagated to the last-level PTE, it might not be true in the case where a mapping changes (2) It increases coherence traffic to the TLBs to a large extent. Since the data caches do not distinguish data from page-table entries, cache coherence messages are relayed to the TLBs upon each update to the data cache contents.

## 4.2.3 DiDi: A Shared TLB Directory

Villavieja et al [21] propose a scalable architectural mechanism that couples shared TLB directory with load/store queue support for lightweight TLB invalidation and eliminates the need for costly IPIs. The scheme has two components - a second-level TLB that acts as a Dictionary Directory (DiDi), and a Pending TLB Invalidation (PTLBI) buffer. DiDi eliminates unnecessary IPIs by tracking the location of every address translation stored on the first-level TLBs of the whole system using the Directory Bitmap. On the other hand, the PTLBI buffer eliminates the overheads of interrupt processing performing the following operations: storing all broadcasted invalidations, injecting a memory barrier into the load/store queue, actually performing the invalidation, and sending acknowledgement back to the DiDi. DiDi lacks support for hardware virtualization. Although it eliminates expensive IPI delivery, it does not eliminate the busy wait on the initiator core waiting for acknowledgements from the slave cores.

#### 4.2.4 HATRIC: Hardware Translation Invalidation and Coherence

Yan Zi et al [24] propose a hardware mechanism called HATRIC to piggyback translation coherence atop existing cache coherence protocols. In a manner similar to UNITD, by adding co-tags (system physical address of the nested page table entry) to translation structures, HATRIC obviates the need for full translation structure flushes by more precisely identifying invalidation targets. HATRIC then exposes these co-tags to the cache coherence protocol to

precisely identify coherence targets and to eliminate VM exits. HATRIC works well in virtualized environments with heterogeneous memories with potentially a large number of host-page remappings. In modern virtualized systems with no heterogeneous memories, we have observed that the host-page remappings are quite infrequent. Instead, we observe a lot of guest-page table remappings and associated overheads as detailed in the background section. However, HATRIC does not support hardware coherence for guest-page table remappings. Moreover, since it tags the TLB entries with the physical address of last-level PTE, it suffers from the same drawback as UNITD - it cannot track changes to intermediate PTEs.

# Chapter 5

# Architecture Description & Evaluation

## 5.1 Context Switch Aware Large TLB

The address translation overhead in virtualized systems comes from one apparent reason, the lack of TLB capacity. If the TLB capacity were large enough, most of page table walks would have been eliminated. The need for a larger TLB capacity is also seen as a recent generation of Intel processors [65] doubled the L2 TLB capacity from the previous generation. Traditionally, TLBs are designed to be small and fast, so that the address translation can be serviced quickly. Yet, emerging applications require much more memory than traditional server workloads. Some of these applications have terabytes of memory footprint, so that TLBs, which were not initially designed for such huge memory footprint, suffer significantly.

Recent work [20] by Ryoo et al. uses a part of main memory to be used as a large capacity TLB. They use 16MB of the main memory, which is negligible considering high-end servers have terabytes of main memory these days. However, 16MB is orders of magnitude higher than today's on-chip TLBs, and thus, it can eliminate virtually all page table walks. This design achieves the goal of eliminating page table walks, but now this TLB suffers

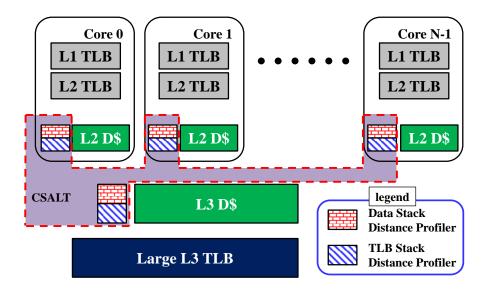

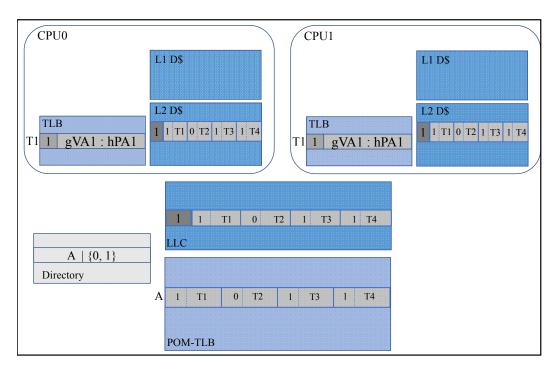

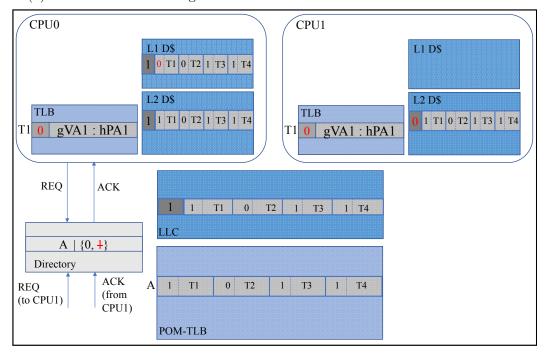

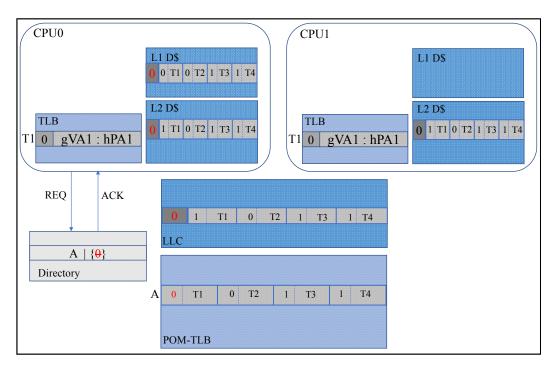

Figure 5.1: CSALT System Architecture

from slow access latency since off-chip DRAM is much slower than on-chip SRAMs. Consequently, they make this high-capacity TLB as addressable, so TLB entries can be stored in data caches. They call this TLB as POM-TLB (Part of Memory TLB) as the TLB is given an explicit address space. CSALT uses the POM-TLB organization as its substrate. It may be noted that CSALT is a cache management scheme, and can be architected over other translation schemes such as conventional page tables.

Figure 5.1 depicts the system architecture incorporating CSALT architected over the POM-TLB. CSALT encompasses L2 and L3 data cache management schemes. The role of the stack distance profilers shown in the figure is described in Section 5.1.1. In the following subsections, we describe the architecture of our Context-Switch Aware Large TLB (CSALT) scheme.

First, we explain the dynamic partitioning algorithm that helps to find a balanced partitioning of the cache between TLB and data entries to reduce the cache contention. In Section 5.1.2, we introduce a notion of "criticality" to improve the dynamic partitioning algorithm by taking into account the relative costs of data cache misses. We also describe the hardware overheads of these partitioning algorithms.

## 5.1.1 CSALT with Dynamic Partitioning (CSALT-D)

Since prior state-of-the-art work [20] does not distinguish data and TLB entries when making cache replacement decisions, it achieves a suboptimal performance improvement. The goal of CSALT is to profile the demand for data and TLB entries at runtime and adjust the cache capacity needed for each type of cache entry.

CSALT dynamic partitioning algorithm (*CSALT-D*) attempts to maximize the overall hit rate of data caches by allocating an optimal amount of cache capacity to data and TLB entries. In order to do so, CSALT-D attempts to minimize interference between the two entry types. Assuming that a cache is statically partitioned by half for data and TLB entries, if data entries have higher miss rates with the current allocation of cache capacity, CSALT-D would allocate more capacity for data entries. On the other hand, if TLB entries have higher miss rates with the current partitioning scheme, CSALT-D would allocate more cache for TLB entries. The capacity partitioning is adjusted at a fixed interval, and we refer to this interval as an epoch. In

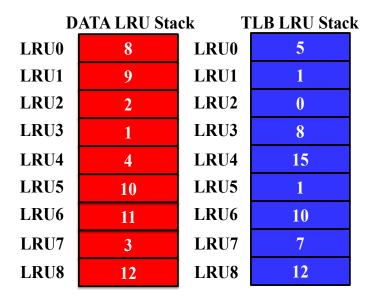

order to obtain an estimate of cache hit/miss rate for each type of entry when provisioned with a certain capacity, we implement a cache hit/miss prediction model for each type of entry based on Mattson's Stack Distance (MSA) algorithm [66]. The MSA uses the LRU information of set-associative caches. For a K-way associative cache, LRU stack is an array of (K+1) counters, namely  $Counter_1$  to  $Counter_{K+1}$ .  $Counter_1$  counts the number of hits to the Most Recently Used (MRU) position, and  $Counter_K$  counts the number of hits to the LRU position.  $Counter_{K+1}$  counts the number of misses incurred by the set. Each time there is a cache access, the counter corresponding to the LRU stack distance where the access took place is incremented.

LRU stack can be used to predict the hit rate of the cache when the associativity is increased/reduced. For instance, consider a 16-way associative cache where we record LRU stack distance for each of the accesses in a LRU stack. If we decrease the associativity to 4, all the accesses which hit in positions LRU4 - LRU15 in the LRU stack previously would result in a miss in the new cache with decreased associativity (LRU0 is the MRU position). Therefore, an estimate of the hit rate in the new cache with decreased associativity can be obtained by summing up the hit rates in the LRU stack in positions LRU0 - LRU3.

For a K-way associative cache, our dynamic partitioning scheme works by allocating certain ways (0: N-1) for data entries and the remaining ways for TLB entries (N: K-1) in each set in order to maximize the overall cache hit rate. For each cache which needs to be dynamically partitioned, we introduce two additional structures: a data LRU stack, and a TLB LRU stack corresponding to data and TLB entries respectively. The data LRU stack serves as a cache hit rate prediction model for data entries whereas the TLB LRU stack serves as as a cache hit rate prediction model for TLB entries. Estimates of the overall cache hit rates can be obtained by summing over appropriate entries in the data and TLB LRU stack. For instance, in a 16-way associative cache with 10 ways allocated for data entries and remaining ways allocated for TLB entries, an estimate of the overall cache hit rate can be obtained by summing over LRU0 - LRU9 in Data LRU stack and LRU0 - LRU5 in the TLB LRU stack.

This estimate of the overall cache hit rate obtained from the LRU stack is referred to as the  $Marginal\ Utility$  of the partitioning scheme [67]. Consider a K-way associative cache. Let the data LRU stack be represented as D\_LRU and the TLB LRU stack be represented as TLB\_LRU. Consider a partitioning scheme P that allocates N ways for data entries and K-N ways for TLB entries. Then the  $Marginal\ Utility$  of P, denoted by  $MU_N^P$  is given by the following equation,

$$MU_{N}^{P} = \sum_{i=0}^{N-1} \mathrm{D\_LRU}(i) + \sum_{j=0}^{K-N-1} \mathrm{TLB\_LRU}(j). \tag{5.1}$$

CSALT-D attempts to maximize the marginal utility of the cache at each epoch by comparing the marginal utility of different partitioning schemes. Consider the example shown in Figure 5.2 for an 8-way associative cache. Suppose the current partitioning scheme assigns N=4 and M=4. At the

## **Algorithm 1** Dynamic Partitioning Algorithm

```

1: \mathbb{N} = \mathbb{N}umber of ways to be allocated for data

2: \mathbb{M} = \mathbb{N}umber of ways to be allocated for TLB

3:

4: for n in N_{min}: K-1 do

5: MU_n = \mathsf{compute\_MU}(n)

6: end for

7:

8: \mathbb{N} = \underset{N}{arg} \max(MU_{N_{min}}, MU_{N_{min}+1}, ..., MU_{K-1})

9: \mathbb{M} = K - \mathbb{N}

```

end of an epoch, the D\_LRU and TLB\_LRU contents are shown in Figure 5.2. In this case, the dynamic partitioning algorithm finds the marginal utility for the following partitioning schemes (not every partitioning is listed):

$$\begin{split} MU_4^{P1} &= \sum_{i=0}^3 \text{D\_LRU}(i) + \sum_{j=0}^3 \text{TLB\_LRU}(j) = 34 \\ MU_5^{P2} &= \sum_{i=0}^4 \text{D\_LRU}(i) + \sum_{j=0}^2 \text{TLB\_LRU}(j) = 30 \\ MU_6^{P3} &= \sum_{i=0}^5 \text{D\_LRU}(i) + \sum_{j=0}^1 \text{TLB\_LRU}(j) = 40 \\ MU_7^{P4} &= \sum_{i=0}^6 \text{D\_LRU}(i) + \sum_{j=0}^0 \text{TLB\_LRU}(j) = 50 \end{split}$$

(5.2)

Among the computed marginal utilities, our dynamic scheme chooses the partitioning that yields the best marginal utility. In the above example, CSALT-D chooses partitioning scheme P4. This is as elaborated in Algorithm 1 and Algorithm 2.

Once the partitioning scheme  $P_{new}$  is determined by the CSALT-D

algorithm, it is enforced globally on all cache sets. Suppose the old partitioning scheme  $P_{old}$  allocated  $N_{old}$  ways for data entries, and the updated partitioning scheme  $P_{new}$  allocates  $N_{new}$  ways for data entries. We consider two cases: (a)  $N_{old} < N_{new}$  and (b)  $N_{old} > N_{new}$  and discuss how the partitioning scheme  $P_{new}$  affects the cache lookup and cache replacement. While CSALT-D has no affect on cache lookup, CSALT-D does affect replacement decisions. Here, we describe the lookup and replacement policies in detail.

Cache Lookup: All K-ways of a set are scanned irrespective of whether a line corresponds to a data entry or a TLB entry during cache lookup. In case (a), even after enforcing  $P_{new}$ , there might be TLB entries resident in the ways allocated for data (those numbered  $N_{old}$  to  $N_{new} - 1$ ). On the other hand, in case (b), there might be data entries resident in the ways allocated for TLB entries (ways numbered  $N_{new}$  to  $N_{old} - 1$ ). This is why all ways in the cache is looked up as done in today's system.

Cache Replacement: In the event of a cache miss, consider the case where an incoming request corresponds to a data entry. In both case (a) and (b), CSALT-D evicts the LRU cacheline in the range  $(0, N_{new} - 1)$  and places the incoming data line in its position. On the other hand, if the incoming line corresponds to a TLB entry, in both case (a) and (b), CSALT-D evicts the LRU-line in the range  $(N_{new}, K - 1)$  and places the incoming TLB line in its position.

Classifying Addresses as Data or TLB: Incoming addresses can be classified as data or TLB by examining the relevant address bits. Since the POM-

## Algorithm 2 Computing Marginal Utility

```

1: N = Input

2: D_LRU = Data LRU Stack

3: TLB_LRU = TLB LRU Stack

4: MU = 0

5:

6: for i in 0: N - 1 do

7: MU += D_LRU (i)

8: end for

9: for j in 0: K - N - 1 do

10: MU += TLB_LRU (j)

11: end for

12: return MU

```

TLB is a memory mapped structure, the cache controller can identify if the incoming address is to the POM-TLB or not. For stored data in the cache, there are two ways by which this classification can be done: i) by adding 1 bit of metadata per cache block to denote data (0) or TLB (1), or ii) by reading the tag bits and determining if the stored address falls in the L3 TLB address range or not. We leave this as an implementation choice. In our work, we assume the latter option as it does not affect metadata storage.

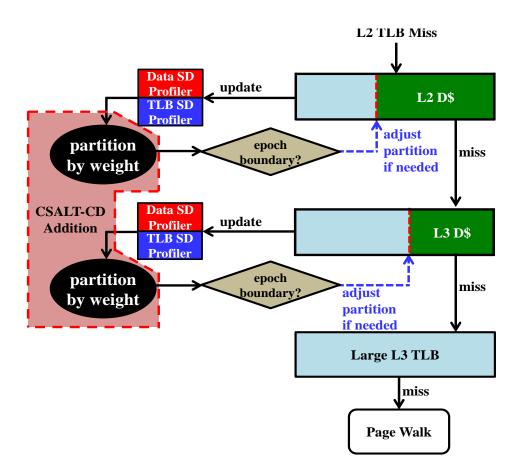

Finally, the overall flow is summarized in Figure 5.3. Each private L2 cache maintains its own stack distance profilers and updates them upon accesses to it. When an epoch completes, it computes marginal utilities and sets up a (potentially different) configuration of the partition between data ways and TLB ways. Misses (and writebacks) from the L2 caches go to the L3 cache which performs a similar update of its profilers and configuration outcome. A TLB miss from the L3 data cache is sent to the L3 TLB. Finally,

Figure 5.2: LRU Stack Example

a miss in the L3 TLB triggers a page walk.

## 5.1.2 CSALT with Criticality Weighted Partitioning (CSALT-CD)